3 Ethernet zrealizowany z wykorzystaniem kabli miedzianych o parach skręconych od 10 Mb/s do 10 Gb/s – sygnały, mechanizmy

3.1 Standard 10BASE-T

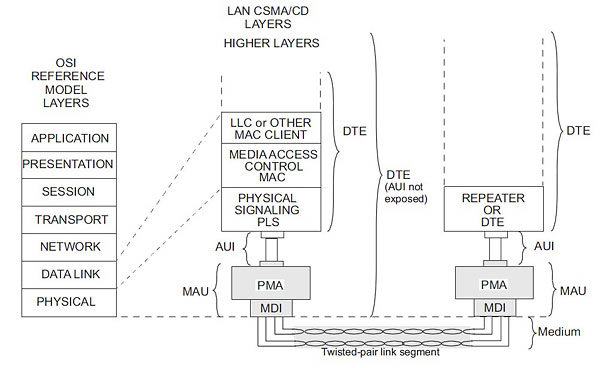

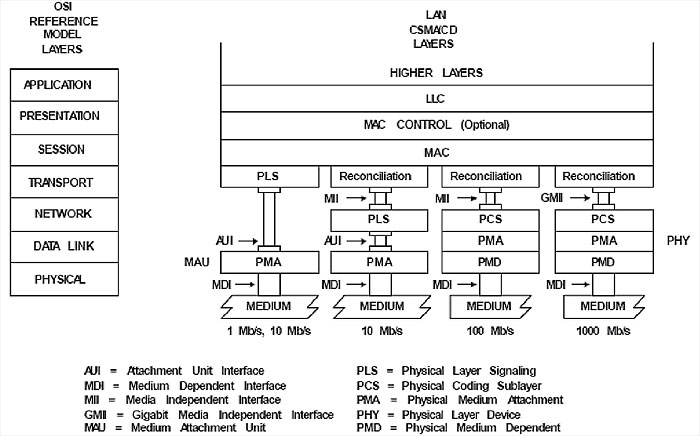

Podstawowym elementem każdego urządzenia zdolnego do pracy z siecią Ethernet jest zespół nadawczo-odbiorczy (ang. Transceiver). Znajduje się on na każdej karcie sieciowej, koncentratorze, przełączniku czy innym urządzeniu, w liczbie odpowiadającej liczbie portów. Złożony jest z wielu bloków funkcjonalnych, odpowiedzialnych za poszczególne etapy przygotowania danych z postaci przechowywanej w komórkach pamięci na sygnały elektryczne przesyłane poprzez kable. Poszczególne bloki funkcjonalne można umiejscowić w modelu ISO/OSI, co przedstawia rysunek (Rys. 7).

Rys. 7 Standard 10BASE-T w modelu ISO/OSI1

Część z tych bloków poddaje się procesowi integracji w złożonych strukturach układów scalonych zawierających w sobie również kontroler czy procesor sygnałowy, zaś pozostałe z nich występują jako dyskretne elementy pełniące specyficzne funkcje. W szczególności układy podwarstwy PLS, a więc odpowiedzialne za kodowanie i współpracę z warstwą MAC były integrowane w układzie kontrolera, zaś podłączone przez styk AUI układy interfejsu zależnego od medium PMA i MDI konstruowane jako układy z elementów dyskretnych bądź hybrydowych. W kontrolerach Ethernet stosowanych w rozwiązaniu 10BASE-T często można spotkać podzespoły potrzebne do obsługi rozwiązań dla kabla koncentrycznego. Bardzo powszechne w połowie lat 90. były karty wyposażone zarówno w gniazda RJ-45 dla skrętki (i współpracujące z nimi elementy), jak i BNC dla cienkiego kabla koncentrycznego. Niektóre firmy, np. 3Com, produkowały karty z trzema interfejsami2, Dodatkowo wyposażano je w piętnastostykowe złącza AUI, przeznaczone pod podłączenia adaptera MAU mocowanego na grubym kablu koncentrycznym. Pod koniec lat 90., w dobie upowszechnienia się standardu 10BASE-T, karty z zamontowanymi dwoma lub trzema różnymi interfejsami straciły na popularności na rzecz tańszych w produkcji kart z tylko jednym interfejsem dla kabla skrętkowego.

3.1.1 Budowa adaptera Ethernet 10BASE-T

Zdjęcie (Fot. 11) przedstawia powszechnie stosowaną w latach dziewięćdziesiątych kartę sieciową ReadyLINK RL2000-PCI produkcji firmy COMPEX, przeznaczoną do pracy w sieciach Ethernet typu 10BASE-2 i 10BASE-T. Konstrukcja tej karty została oparta na zaleceniach firmy Novell, zapewniając zgodność na poziomie sterowników ze standardem NE20003.

Fot. 11 Karta sieciowa - Kontroler Ethernet 10BASE-T/10BASE-2 - COMPEX RL2000-PCI [fot. własna]

Na zdjęciu (Fot. 11) oznaczyłem cyframi najważniejsze podzespoły:

- złącze magistrali PCI4 – punkt styku kontrolera Ethernet RL2000 z magistralą systemową komputera,

- kontroler Ethernet RL2000,

- pamięć RAM5 kontrolera Ethernet,

- rezonator kwarcowy, stabilizujący pracę generatora sygnału zegarowego,

- pamięć EEPROM6 – przeznaczoną do przechowywania informacji o konfiguracji karty (dane na temat wybranego PMD, a także konfiguracji adresu i przerwania dla złącza PCI,

- zespół dwóch transformatorów liniowych wraz z filtrem dolnoprzepustowym dla 10BASE-T,

- przetwornica zasilania prądu stałego o napięciu 5 V (ang. DC/DC Converter) przeznaczoną do zasilania układu PMD dla 10BASE-2,

- zespół trzech transformatorów o przekładni 1:1 (stanowiący odpowiednik styku AUI stosowanego 10BASE-5) dla dwukierunkowej transmisji pomiędzy kontrolerem a blokiem nadawczo-odbiorczym dla 10BASE-2,

- układ nadawczo-odbiorczy PMD dla 10BASE-2,

- gniazdo BNC do podłączenia trójnika dla 10BASE-2, wraz z towarzyszącymi elementami – kondensatorem kompensującym7, diodą zenera8 oraz warystorem9,

- gniazdo RJ-45 do podłączenia kabla skrętkowego CAT3 10BASE-T,

- diody LED Link (sygnalizacja połączenia) oraz Activity (aktywność łącza).

Na karcie znajdują się również niewykorzystane miejsca na zatrzask magistrali adresowej 74HCT373 oraz 32kB pamięć EPROM 27C51210.

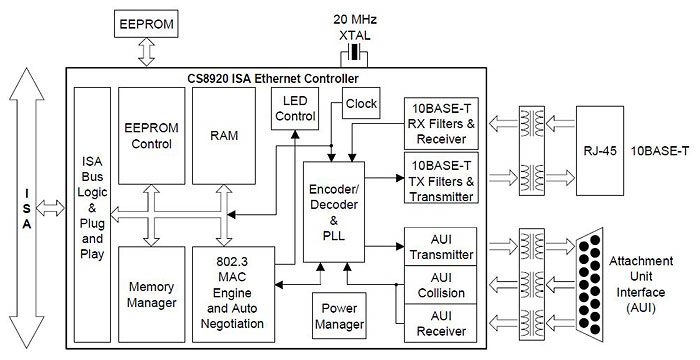

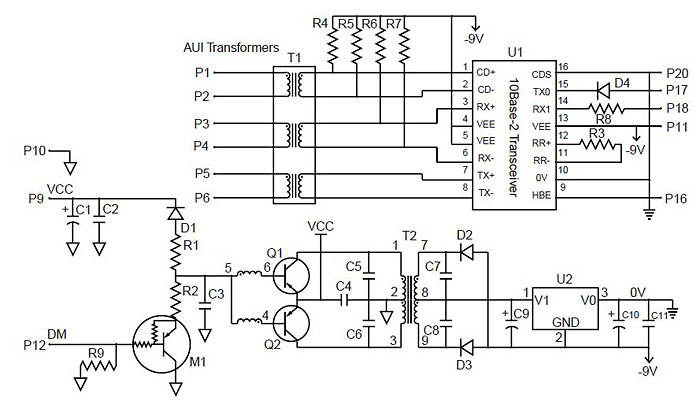

Rys. 8 Schemat blokowy kontrolera 10BASE-2/10BASE-T11

Rysunek 8 przedstawia uproszczony schemat blokowy karty o typowej budowie, posiadającej dwa interfejsy zależne od medium dla kabla skrętkowego ze złączem RJ-45 i kabla koncentrycznego poprzez układ MAU włączony poprzez AUI lub zintegrowany.

Blok współpracy z medium koncentrycznym składa się z elementów oznaczonych na zdjęciu numerami 7, 8, 9 i 10. Przykładowy schemat rozwiązania takiego układu przedstawia rysunek (Rys. 9). W tym układzie linia P3-4 jest linią odbiorczą, P5-6 linią nadawczą, zaś P1-2 służy do wykrywania kolizji. Wszystkie te trzy linie podłączone do kontrolera Ethernet stanowią punkt styku AUI, który w rozwiązaniu 10BASE-5 był przedłużany do 15 metrów w celu wyniesienia transceivera z obudowy komputera w pobliże kabla magistrali. Elementy skupione wokół tranzystorów M1,Q1,Q2 wraz z uzwojeniem pierwotnym transformatora T2 składają się na układ przetwornicy napięcia. Napięcie prostowane w układzie dwupołówkowego prostownika jest stabilizowane przez monolityczny stabilizator szeregowy U2 do wartości -9V.

Rys. 9 Schemat układu podłączenia do medium w 10BASE-212

Uzyskane w ten sposób ujemne napięcie, odniesione do wyizolowanej masy, służy wyłącznie do zasilania układu transceivera U1. Widoczna na schemacie dioda zenera D4 służy do detekcji wzrostu napięcia w kablu, świadczącym o zaistnieniu kolizji13.

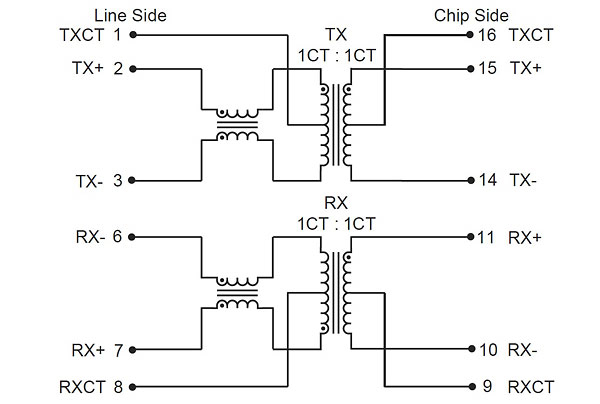

Układ przyłączenia do medium w postaci kabla o parach skręconych jest znacznie uproszczony w stosunku do starszych rozwiązań (Fot. 12). Składa się z dwóch elementów, oznaczonych numerami 6 i 11 zespołu dwóch transformatorów o przekładni 1:1 (analogicznie jak w rozwiązaniach 10BASE-2 i 10BASE-5) i filtrów dolnoprzepustowych – dławików zakłóceń współbieżnych (Rys. 10) oraz gniazda RJ-45. Schemat połączeń wewnętrznych przykładowego układu hybrydowego został zamieszczony na poniższym rysunku. Różnorodne układy hybrydowe, złożone z transformatorów i filtrów, a w szczególności sposób ich nawinięcia i połączenia, chronione są prawem patentowym14.

Rys. 10 Układ dopasowania linii – transformator symetryzujący i filtr dolnoprzepustowy15

Transformatory i dławiki nawinięte są drutem emaliowanym na ferrytowych rdzeniach toroidalnych (pierścieniowych). Odczepy uzwojeń transformatorów od strony kabla służą do wyrównania potencjału par symetrycznie względem masy. Połączenia tego dokonuje się, zwierając (dla prądu wielkiej częstotliwości) środek uzwojenia poprzez kondensator do masy. Odczepy uzwojeń po stronie układu kontrolera służą do dostarczenia napięcia zasilającego stopień wyjściowy nadajnika, pracujący zwykle w symetrycznym układzie z otwartym drenem. Dla odbiornika układu tą samą drogą dostarcza się napięcia polaryzującego różnicowy wzmacniacz wejściowy.

Fot. 12 Styk kontrolera z medium – Transceiver, transformator, gniazdo, wtyk, kabel [fot. własna]

Filtry dolnoprzepustowe są nawinięte bifilarnie16, zapewniając maksymalne tłumienie zakłóceń współbieżnych (zaindukowanych w równej wartości na obu żyłach pary) oraz tłumią wyższe harmoniczne sygnału 10MHz ze względu na wymogi kompatybilności elektromagnetycznej17. Standard 10BASE-T precyzuje szczegółowo wymagania dotyczące tłumienia wyższych harmonicznych18 (Tab. 3).

|

cz. harmoniczna |

2 i 3 |

4 i 5 |

6 i 7 |

> 7 |

|

min. tłumienie |

20 dB |

30 dB |

40 dB |

50 dB |

Tab. 3 Wymagane tłumienie wyższych harmonicznych sygnału w 10BASE-T

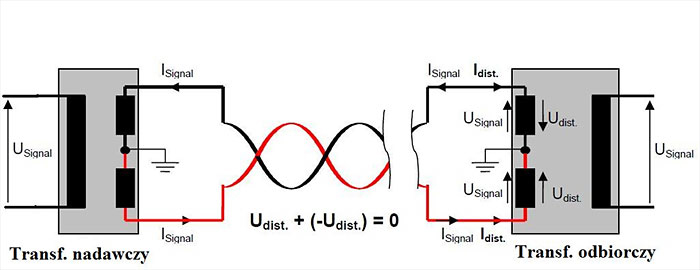

Bardzo istotną cechą transformatorów dopasowujących19 jest galwaniczna separacja (dla prądu stałego) kabla od układu nadawczo-odbiorczego, co pozwala na uniknięcie przepływu prądów wyrównawczych pomiędzy współpracującymi urządzeniami20.

Na fotografii (Fot. 13) można zobaczyć, że cały układ dopasowania mieści się w niewielkiej obudowie z tworzywa, rozstawem doprowadzeń odpowiadającej typowym układom scalonym w obudowach DIL16. Wnętrze przykładowego zespołu transformatorów i filtrów prezentuje poniższa fotografia. Ponieważ w celu otwarcia wypełnionego żywicą epoksydową układu hybrydowego musiałem użyć siły, część uzwojeń uległa uszkodzeniu, jednakże fotografia pozwala zaobserwować, że transformatory mają średnicę ok. 3,5mm zaś dławiki 2mm. Widać też bifilarne nawinięcie dławików parą przewodów czerwony-zielony.

Fot. 13 Wnętrze hybrydowego układu dopasowania linii firmy PULSE, w górnej części – skala w mm [fot. własna]

W urządzeniach wieloportowych, np. przełącznikach stosuje się układy hybrydowe, przeznaczone do obsługi czterech portów, zawierające w sobie komplet ośmiu transformatorów i ośmiu dławików21.

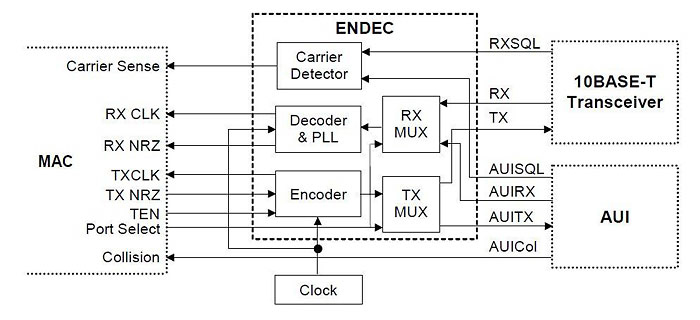

Rys. 11 Schemat blokowy kodera/dekodera Ethernet dla 10BASE-T/10BASE-2/522

Na powyższym rysunku prezentującym wewnętrzną organizację modułu kodera/ dekodera Manchester23 (Rys. 11) uwidoczniono miejsce doprowadzenia sygnału zegarowego (ang. Clock) i układ wykrywania sygnału w linii (ang. Carrier Detect). Enkoder (ang. Encoder) służy do zakodowania danych 8-bitowych w szeregowy ciąg znaków po stronie nadawczej, zaś dekoder (ang. Decoder) realizuje funkcję odwrotną po stronie odbiorczej.

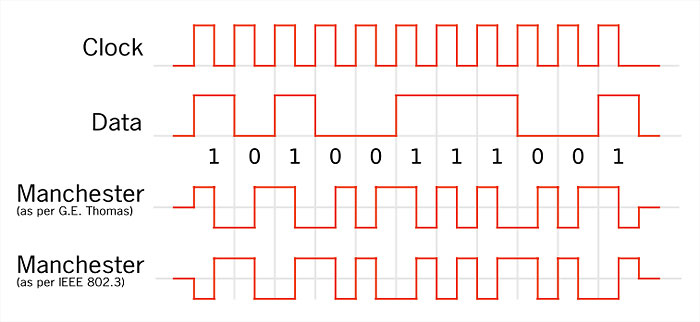

Rys. 12 Schemat poglądowy kodowania Manchester24

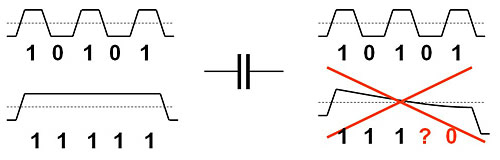

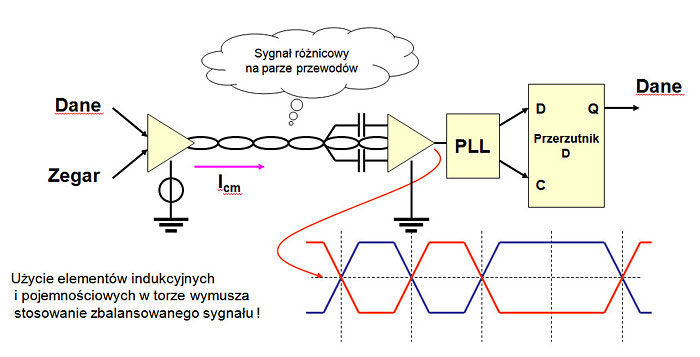

Zastosowane kodowanie Manchester, dzięki istnieniu zmiany stanu w każdym cyklu zegara transmisyjnego (Rys. 12), pozwala na synchronizację odbiornika bez konieczności przesyłania dodatkową linią sygnału zegarowego. Fakt przesyłania sygnału ciągle zmiennego, bez momentów o stałym poziomie napięcia pozwala na przeniesienie danych przez transformatory i kondensatory (Rys. 13) – elementy niezbędne do konstrukcji łącza bazującego na transmisji sygnałów elektrycznych, bez ryzyka przekłamania informacji. Do odtworzenia sygnału zegara po stronie odbiorczej służy układ pętli synchronizacji fazowej PLL25.

Rys. 13 Ilustracja odkształcenia przebiegu zakodowanego kodem Manchester i niezakodowanego26

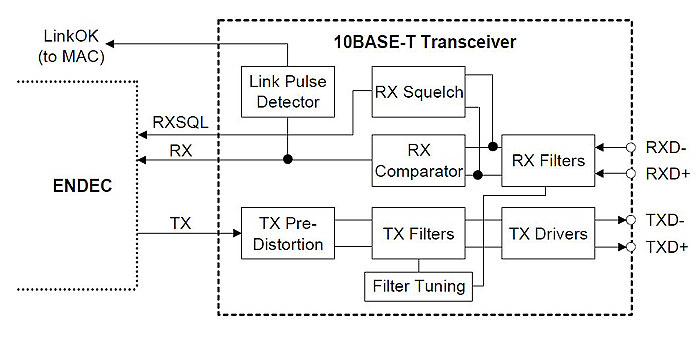

Pozostałe dwa bloki zaznaczone na rysunku (Rys. 11) – to multipleksery (oznaczone TX-MUX w torze nadawczym i RX-MUX w torze odbiorczym) – elementy niezbędne do przełączenia drogi sygnału w zależności od wybranego medium transmisyjnego. W logicznym ujęciu stanowią miejsce styku pomiędzy warstwą niezależną od medium (PMI) a zależną od medium (PMD). W torze przeznaczonym do współpracy ze skrętką (Rys. 14) można wyróżnić zespół filtrów aktywnych27 zarówno po stronie nadawczej, jak i odbiorczej.

Rys. 14 Schemat blokowy układu nadawczo odbiorczego dla 10BASE-T28

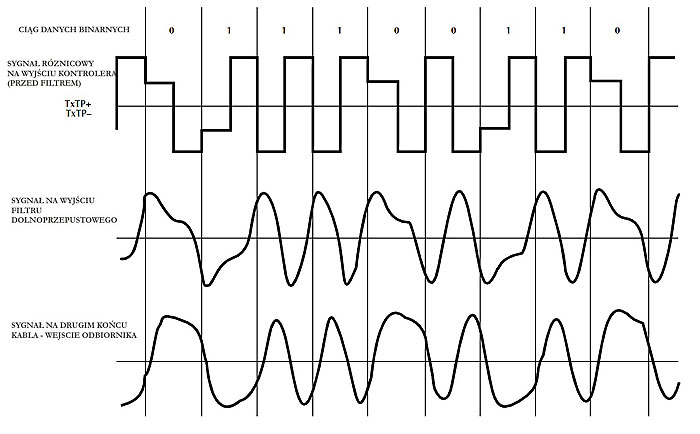

Ich zadaniem jest stłumienie wyższych harmonicznych przebiegu nadawanego i odseparowanie zakłóceń w torze odbieranym. Kształt przebiegu w torze, przed filtrem nadawczym, za filtrem nadawczym i na drugim końcu linii za filtrem odbiorczym, bezpośrednio na wejściu odbiornika ilustruje rysunek (Rys. 15).

Rys. 15 Zniekształcenie przebiegu nadawanego przez filtr dolnoprzepustowy i kabel kategorii trzeciej29

Stopień wyjściowy nadajnika (ang. TX Driver) musi zapewnić stały poziom sygnału nadawanego na liniach TX+ i TX-, o amplitudzie na poziomie ±2,5 V (maksymalna dopuszczalna wartość to 2,8 V). Wartość taka jest niezbędna dla uzyskania na drugim końcu kabla o długości 100 m i przekroju żył w zakresie 0,404-0643 mm napięcia na wejściu odbiornika nie niższego niż +/- 350 mV. Stopień wejściowy odbiornika (ang. Rx Filter & Receiver) wyposażony jest w układ automatycznej regulacji wzmocnienia, pozwalający zachować stały, optymalny punkt pracy dekodera bez względu na długość kabla.

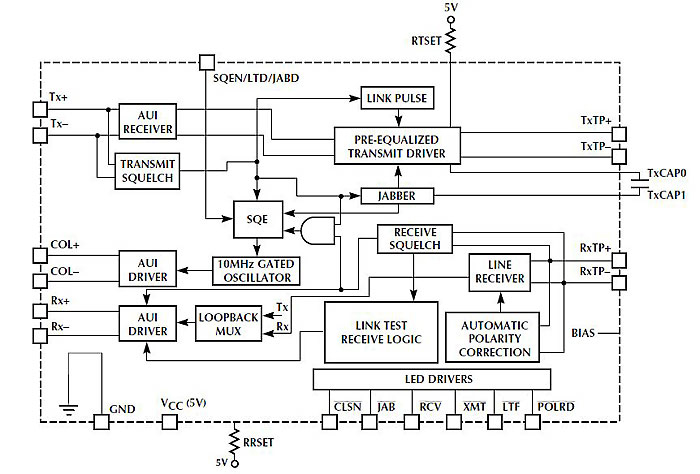

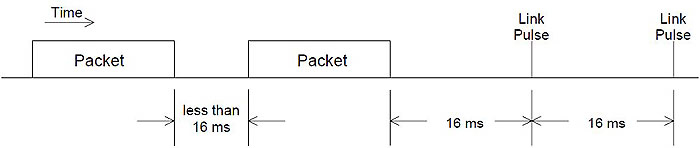

W stanie bezczynności, gdy nie są przesyłane dane, układ nadajnika wysyła impulsy LP (ang. Line Pulse), aby poinformować odbiornik o gotowości do wysyłania danych i utrzymania w odbiorniku informacji o poziomie napięcia odbieranych sygnałów, niezbędnej dla układu automatycznej regulacji wzmocnienia. Odpowiedzialny jest za to układ generatora impulsów LP, uwidoczniony na bardziej szczegółowym schemacie nadajnika 10BASE-T (Rys. 16).

Rys. 16 Schemat mikroukładu MAU dla 10BASE-T30

Impulsy LP wysyłane są co 16 ms z dokładnością +/- 8 ms, zaś ich czas trwania wynosi średnio 2 µs. Zależności czasowe, pomiędzy ramkami informacyjnymi a impulsami stanu łącza prezentuje rysunek (Rys. 17).

Rys. 17 Odstęp pomiędzy ramkami a impulsy stanu łącza31

W przypadku wykrycia kolizji przy użyciu mechanizmu CSMA/CD karta uruchamia układ JABBER (Rys. 16) w celu wprowadzenia do toru sygnału zakłócającego, pozwalającego na szybkie wykrycie kolizji przez pozostałe podłączone do tego samego segmentu sieci stacje.

Z elektrycznego punktu widzenia transmisja sygnału cyfrowego za pomocą pary przewodów, gdzie przebiegi w sąsiednich żyłach pary są symetryczne względem zera napięcia (Rys. 18), powoduje mniejszą podatność sygnału na zakłócenia zewnętrzne. Dodatkowe skręcenie przewodów powoduje zmniejszenie rozpraszania sygnału wokół kabla, a tym samym mniejszą emisję zakłóceń emitowanych do środowiska.

Rys. 18 Idea przesyłania sygnałów różnicowych za pomocą pary przewodów32

Rysunek 19 ilustruje zjawisko kompensacji prądów zakłócających, zaindukowanych w równej wartości na obu przewodach pary skręconej (ich równa wartość wynika z bliskiej lokalizacji i jednakowego położenia w stosunku do linii sił zewnętrznego pola zakłócającego). Umiejscowiony z lewej strony transformator nadawczy zamienia napięcie odniesione względem masy na parę napięć o równej wartości, lecz przeciwnych znakach, odniesionych do masy. Napięcia te wywołują przepływ prądu w pętli, zawierającej na drugim końcu skrętki uzwojenie wtórne transformatora odbiorczego z uziemionym odczepem środkowym. Na uzwojeniu wtórnym uzyskuje się sygnał o kształcie odpowiadającym pobudzeniu uzwojenia pierwotnego transformatora nadawczego, o zmniejszonej przez straty (tłumienie kabla, straty w rdzeniach transformatorów) amplitudzie. Zaindukowane sygnały zakłócające docierają do uzwojenia transformatora odbiorczego, na oba zaciski z jednakową amplitudą i znakiem, co powoduje wzajemne ich wytłumianie.

Rys. 19 Wytłumianie zakłóceń współbieżnych, zaindukowanych w parze skręconej33

3.1.2 Metodyka wykonywania pomiarów oscyloskopowych sygnałów elektrycznych przesyłanych w sieciach Ethernet

Zapraszam do lektury podrozdziału poświęconego metodyce pomiarów oscyloskopowych umieszczonego na oddzielnej stronie.

3.1.3 Pomiary sygnałów w sieci Ethernet 10BASE-T

Oscylogram zamieszczony na rysunku 22 obrazuje wynik rejestracji całej, pojedynczej ramki Ethernetowej w sieci 10BASE-T. W celu zarejestrowania ramki o znanych parametrach użyłem polecenia PING z opcja –l 128 –t.

Rys. 22 Ethernet 10BASE-T Rejestracja ramki 170 bajtowej ICMP, PING –l 128 [opracowanie własne]

Z oscylogramu, przy podstawie czasu 20 µs/działkę, można odczytać czas trwania ramki równy 146 µs, wartość amplitudy ~2 V. Rysunek pozwala zauważyć, że przebieg jest modulowany, o czym świadczy nierównomierne wypełnienie, oraz że w czasie pomiędzy ramkami informacyjnymi w linii występuje brak sygnału. Znając teoretyczną długość ramki Ethernet z ładunkiem (ang. Payload) protokołu ICMP równą 170 bajtów wraz z ośmioma bajtami preambuły i czterema sumy kontrolnej równą 1456 bitów, jak również czas nadania pojedynczego bitu równy 100 ns wnioskuję, że czas trwania ramki powinien wynosić 145,6 µs. Zarejestrowany wynik 146 µs, jako różny o około 0,3% od spodziewanej wartości, biorąc pod uwagę dokładność zegara karty, zegara wzorcowego oscyloskopu i precyzji ustawienia markerów, uznaję za wystarczająco precyzyjny.

Przy dwudziestokrotnym skróceniu podstawy czasu, do 1 µs/działkę można już zaobserwować strukturę ramki, wyodrębnić charakterystyczne pola, np.: preambułę, pola adresowe i sumę kontrolną. Wyraźnie widoczne są pojedyncze cykle sygnału podstawowego niosące bity informacyjne (Rys. 23). Pomiar ten, jak również kolejne, zostały wykonane przed transformatorem, bezpośrednio na wyjściu linii Tx+/Tx- układu transceivera. Miało to na celu jak najwyraźniejsze zobrazowanie sposobu kodowania bitowego.

Rys. 23 Preambuła ramki Ethernet 10BASE-T i początek pola adresu [opracowanie własne]

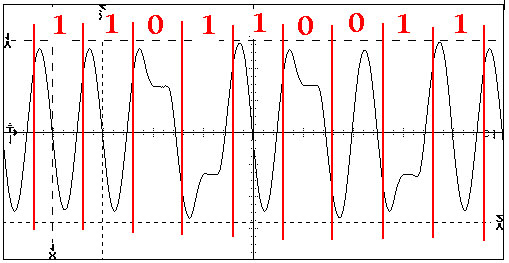

Oscylogram zamieszczony na rysunku 24 prezentuje dziewięć bitów danych zarejestrowanych przy podstawie czasu 100 ns/działkę. Korzystając z funkcji pomiarowych oscyloskopu, ustawiając znaczniki x1 i x2 w dwóch kolejnych punktach przebiegu o wartości 0 V, odczytałem czas trwania jednego okresu, w którym nie zachodziła modulacja równy 100 ns i związaną z nim częstotliwość sygnału bazowego równą 10 MHz. Analizując kształt zarejestrowanego przebiegu, można wywnioskować, że jest on odwrócony w polaryzacji i przesunięty o pół okresu.

Rys. 24 Dziewięć bitów pola danych ramki Ethernet 10Baset-T [opracowanie własne]

Po odwróceniu przebiegu według osi OY i nałożeniu siatki równoodległych linii (co 100 ns) możliwe jest odczytanie dziewięciu kolejnych bitów o wartościach ‘110110011’ (Rys. 25).

Rys. 25 Dekodowanie bitów informacyjnych w ramce 10BASE-T [opracowanie własne]

Zmniejszając dwukrotnie szybkość podstawy czasu do 50 ns/działkę, udało się wyraźnie zaobserwować czas trwania kodowania bitu jako opóźnienie 30 ns co odpowiada przesunięciu fazy sygnału o 120° lub braku takiego przesunięcia (Rys. 26).

Rys. 26 Modulacja fazy fali nośnej 10MHz w ramce Ethernet 10BASE-T [opracowanie własne]

W celu zobrazowania charakterystycznej cechy transmisji w Ethernecie 10BASE-2, jaką jest bezczynność pomiędzy ramkami informacyjnymi skorzystałem z rejestracji dwukanałowej. W kanale pierwszym zarejestrowałem sygnał z pary 1-2 zaś w drugim z pary 3-6. W celu wymuszenia ruchu z odstępami użyłem cyklicznie emitowanych ramek protokołu ICMP wyzwolonych za pomocą polecenia „PING –l 64 –t”. Zarejestrowany oscylogram obrazuje zarówno długość ramek jak i wyraźnie widoczne odstępy w czasie bezczynności. Ponadto możliwe jest zmierzenie czasu odpowiedzi na PING przy użyciu markerów x1 i x2, ustawionych na końcach ramek żądania i odpowiedzi. Wyniki tych pomiarów prezentuje rysunek (Rys. 27). W celu zobrazowania faktu wykorzystywania do transmisji w 10BASE-T tylko dwóch par (z dostępnych czterech) skorzystałem z rejestracji czterokanałowej. Kanał pierwszy posłużył do rejestracji sygnału z pary 1-2, drugi pary 3-6, trzeci 4-5 zaś czwarty pary 7-8. Wyniki pomiaru podczas dwukierunkowej transmisji danych przedstawia rysunek (Rys. 28).

Rys. 27 Bezczynność i transmisja w 10BASE-T [opracowanie własne]

Rys. 28 Rejestracja sygnału 10BASE-T w czterech parach kabla [opracowanie własne]

Ostatnim pomiarem, zrealizowanym dla sieci 10BASE-T była próba zarejestrowania impulsów Link Pulse w czasie bezczynności łącza. Odstęp czasowy pomiędzy trwającymi średnio 2,5 µs impulsami wyniósł 16,32 ms, co mieści się w granicach standardu i błędu pomiarowego. Wynik pomiaru prezentuje oscylogram zamieszczony na rysunku 29. Pojedynczy impuls LP, jego kształt i parametry zilustrowane są na rysunku 30.

Rys. 29 Impulsy LP (Line Pulse) przy braku transmisji w Ethernecie 10BASE-T [opracowanie własne]

Rys. 30 Pojedynczy impuls LP [opracowanie własne]

3.2 Standard 100BASE-T

3.2.1 Budowa kontrolera Ethernet 100BASE-T

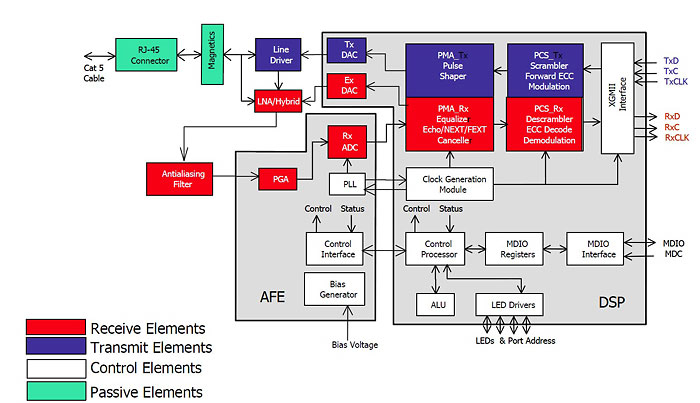

Rozwój standardu Ethernet w kierunku większej szybkości postępował równolegle do zwiększania skali integracji układów mikroprocesorowych i pamięciowych. Wszystkie bloki funkcjonalne, odpowiedzialne za kolejne etapy przetwarzania danych, począwszy od odebrania ich z magistrali komputera aż do wytworzenia impulsów elektrycznych w kablu skrętkowym, zostały zintegrowane w pojedynczym układzie scalonym (w dalszym ciągu poza układem karty pozostały transformatory, pamięć konfiguracji i generator wzorcowy). Poniższa fotografia przedstawia popularną kartę sieciową produkcji firmy Intel, zdolną do pracy w standardach 10BASE-T i 100BASE-TX.

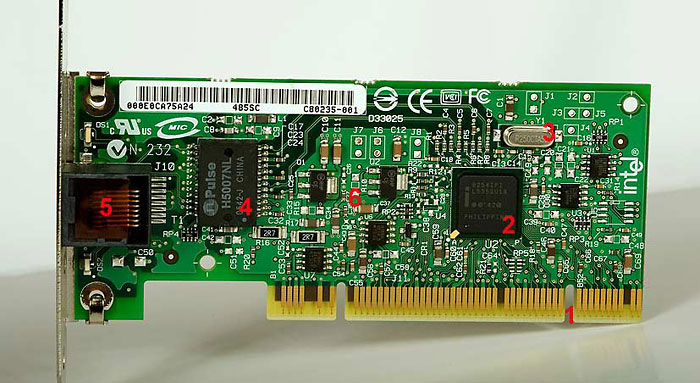

Fot. 22 Karta sieciowa – kontroler Ethernet 10/100BASE-T – INTEL PRO 100 [fot. własna]

Na fotografii (Fot. 22) oznaczyłem cyframi następujace elemnty:

- złącze magistrali PCI,

- zintegrowany kontroler Ethernet,

- hybrydowy, termokompensowany generator kwarcowy 25 MHz,

- hybrydowy zespół transformatorów i filtrów PULSE H1012,

- gniazdo RJ-45.

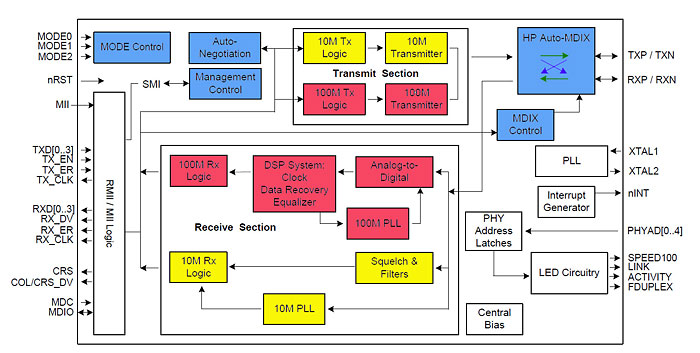

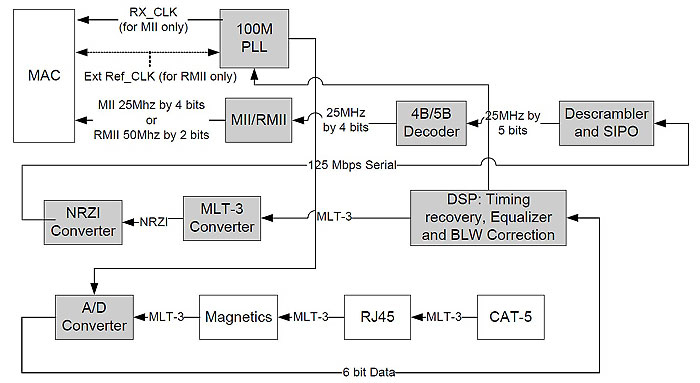

Rys. 31 Schemat blokowy kontrolera Ethernet 10/100 SMSC LAN870034

Na zamieszczonym schemacie blokowym (Rys. 31) można wyróżnić zarówno elementy znane z rozwiązania 10BASE-T (oznaczone kolorem żółtym):

- 10M TX logic – układ kodera Manchester,

- 10M TX transmitter – nadajnik linii,

- squelch & filters – układ filtra aktywnego dla 10 Mb/s,

- 10M PLL – pętla synchronizacji fazowej 10 MHz,

- 10M Rx Logic – układ dekodera Manchester;

jak i nowe elementy, niezbędne do realizacji transmisji 100BASE-TX (oznaczone kolorem czerwonym):

- 100M TX Logic – zespół złożony z enkodera 4B/5B35, skramblera36 z układem PISO37, konwertera NRZI38 oraz kodera MTL-339,

- 100M Transmiter – stopień wyjściowy wraz z filtrem dla 100BASE-TX,

- Analog to Digital – przetwornik analogowo cyfrowy w torze odbiorczym,

- 100M PLL – pętla synchronizacji fazowej 25 MHz,

- DSP System Clock data Recovery Equalizer – procesor sygnałowy, dokonujący odzyskiwania sygnału zegarowego z odebranego przebiegu,

- 100M RX-Logic – zespół złożony z dekodera MTL-3, deskramblera z SIPO40 i dekodera 5B/4B

oraz elementy kontrolne sterowania autonegocjacją i Auto-MDIX (kolor niebieskim).

Ze względu na konieczność współdziałania elementów dwóch standardów w układzie pojawiły się bloki funkcjonalne odpowiedzialne za autonegocjację (ang. Autonegotiation) oraz elementy odpowiedzialne za wykrywanie mapy połączeń kabla (HP Auto-MDIX), które będą opisane w dalszej części niniejszej pracy. Również z tego powodu transformatory linii musiały zostać dostosowane do transmisji sygnałów o wyższych częstotliwościach41.

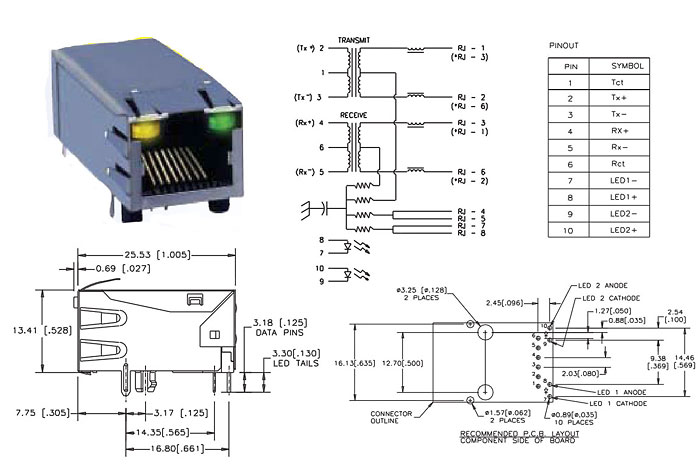

Elementy kart sieciowych 100BASE-T na przestrzeni ponad dziesięciu lat ewoluowały w kierunku coraz większej skali integracji i minimalizacji poboru mocy. Obecnie możliwe jest zarówno zawarcie w pojedynczym układzie scalonym kontrolera obsługującego nawet 16 portów Ethernet 10/100, jak i wykonanie gniazda RJ-45 ze zintegrowanymi transformatorami i filtrami w celu zaoszczędzenia miejsca42 (Rys. 32).

Rys. 32 Gniazdo RJ-45 zintegrowane z filtrem i transformatorem43

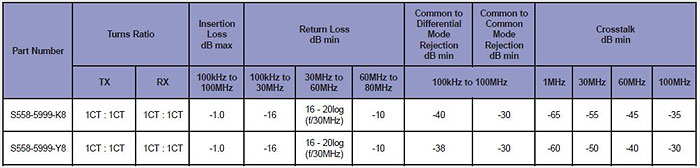

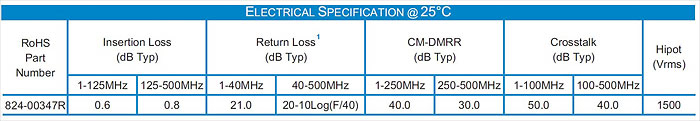

Ze względu na nieznaczne zwiększenie zakresu częstotliwości pracy charakterystyka tłumienia w funkcji częstotliwości nie uległa zmianie, jednakże wprowadzenie możliwości stosowania mechanizmu HP Auto-MDIX wymusiło unifikację układów w torze nadawczym i odbiorczym. Parametry przykładowego układu hybrydowego dla 100BASE-T prezentuje tabela (Tab. 4).

Tab. 4 Zestawienie parametrów elektrycznych transformatorów hybrydowych 44

Szczytowym osiągnięciem miniaturyzacji układów sieciowych do końca 2008 roku było wbudowanie całego, kompletnego kontrolera Ethernet 10/100 wraz elementami towarzyszącymi do gniazda RJ-45 o nieznacznie powiększonym jednym wymiarze45. Rozwiązanie takie proponuje firma Digi International z USA (Fot. 23). Do wbudowania kontrolera Ethernet wraz z gniazdem wystarczyła objętość 5 cm3.

Fot. 23 Kompletny kontroler Ethernet 100BASE-T zintegrowany z gniazdem RJ-45 [DIGI, 2008]

3.2.2 Droga sygnału nadawanego

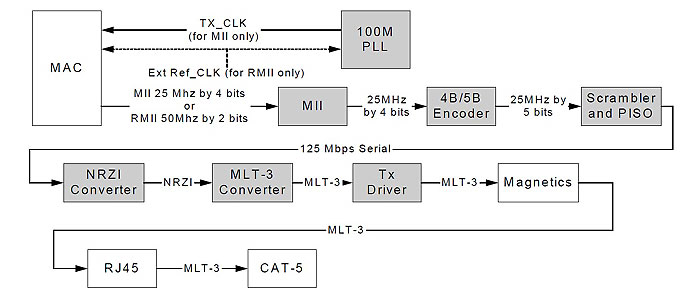

Rys. 33 Droga sygnału 100Mb/s podczas nadawania46

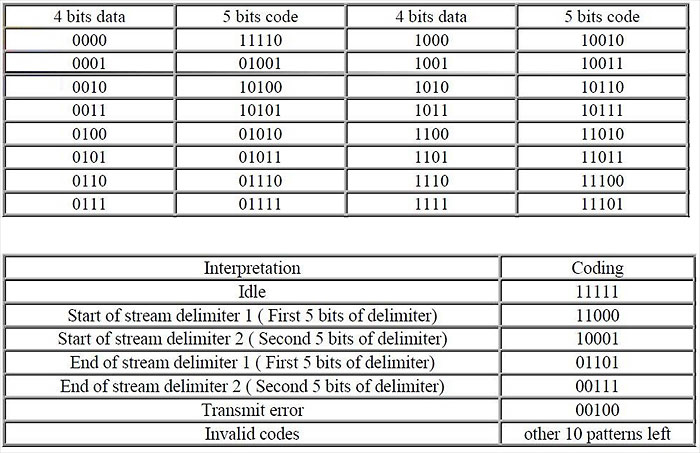

Dane przeznaczone do wysłania z prędkością 100 Mb/s dzielone są wstępnie na połówki bajtów, o długości czterech bitów (Rys. 33). Następnie połówki bajtów kodowane są przy użyciu kodu 4B/5 B do postaci pięciobitowej.

Rozwiązanie to ma na celu wyeliminowanie możliwości występowania długich ciągów o tej samej wartości bitowej mogącej powodować przekłamania, trudność z synchronizacją czy nierównomierne obciążenie układów nadawczych. Dodatkowo, dzięki nadmiarowości znaków istnieje możliwość przesyłania symboli mających znaczenie sygnalizacyjne (Tab. 5). Koder / Dekoder 4B/5B logicznie umiejscowiony jest w podwarstwie PCS47.

Tab. 5 Tablica kodowa 4B5B, kody znaków i sterujące kody specjalne48

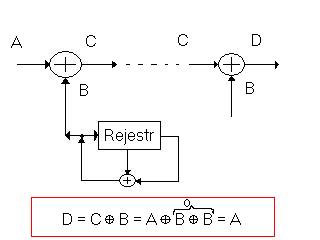

Pięciobitowe słowa przekazywane są z prędkością 25MHz do układu skramblera, gdzie następuje ich zmieszanie z ciągiem pseudolosowym (Rys. 34).

Rys. 34 Ilustracja działania skramblera i deskramblera49

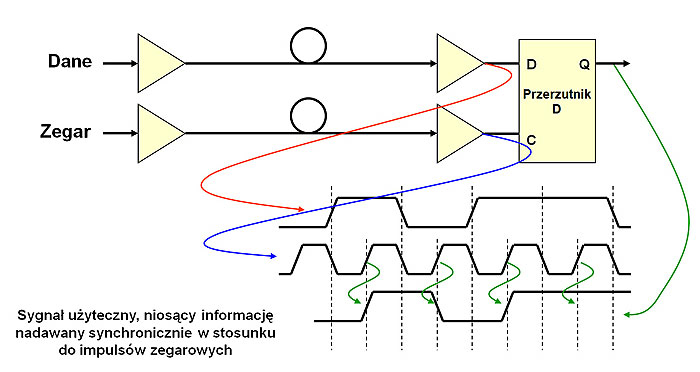

Kolejnym etapem przygotowania danych do wysyłki jest przetworzenie ich na postać szeregową, jednobitową i wysłanie go w takt impulsów zegarowych, synchronizujących transmisję. Funkcję tę spełnia układ PISO.

Rys. 35 Dodawanie sygnału zegarowego do sygnału danych50

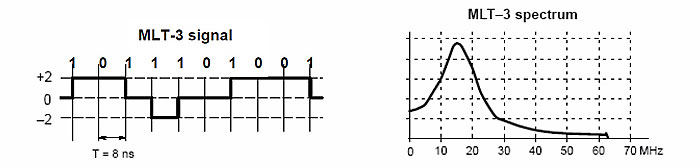

Jednobitowy strumień informacji o prędkości 125 Mb/s poddawany jest następnie kodowaniu NRZI, a następnie zamieniany na kod trójwartościowy. Układ kodera MLT-3 wytwarza dwa przebiegi (Rys. 36 przedstawia jeden z sygnałów), o odwróconej względem siebie polaryzacji (dla linii TX+ i TX-) w celu zasilenia różnicowej pary nadajnika linii.

Rys. 36 Ilustracja działania kodera MLT-3 oraz widmo zakodowanego sygnału51

Ostatecznie zakodowany sygnał przekazywany jest do układu stopnia końcowego, w którym otrzymuje zgodne z normą wartości napięć. Po przejściu przez filtr aktywny, transformator symetryzujący i filtr pasywny sygnał elektryczny o amplitudzie 2 Vp-p52, pozbawiony wyższych częstotliwości harmonicznych i odseparowany galwanicznie od masy układu nadawczego dostarczany jest do złącza RJ-45.

3.2.3 Droga sygnału odbieranego

Schematyczny przebieg sygnału w układzie odbiorczym przedstawia rysunek 37.

Rys. 37 Droga sygnału 100 Mb/s podczas odbioru53

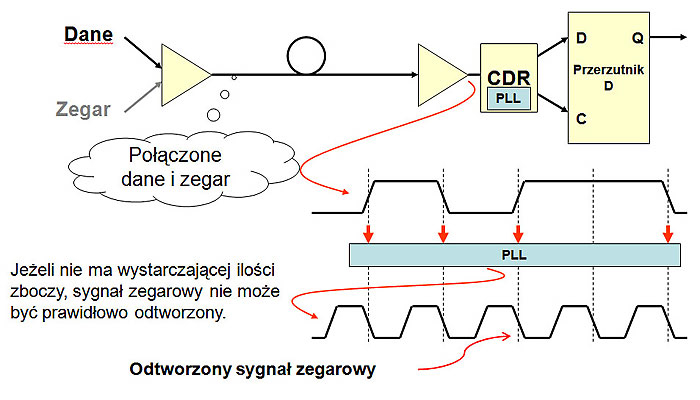

Sygnał o amplitudzie stłumionej poprzez kabel dostarczany jest poprzez filtr zakłóceń współbieżnych i transformator do wzmacniacza wejściowego. Następnie, po wzmocnieniu do akceptowalnej przez przetwornik analogowo-cyfrowy wartości i wstępnym odfiltrowaniu zakłóceń, podlega cyfrowej obróbce. Rezultatem przetwarzania D/A są sześciobitowej rozdzielczości próbki. W pierwszej kolejności z sygnału odzyskuje się i synchronizuje sygnał zegarowy. Odpowiada za to procesor sygnałowy sprężony z pętlą synchronizacji fazowej (Rys. 38).

Rys. 38 Ilustracja procesu odzyskiwania sygnału zegara za pomocą pętli PLL54

Następnie w takt zegara sygnał przechodzi przez kolejne etapy dekodowania:

- Dekoder MTL-3, na którego wyjściu uzyskuje się 125 Mb/s jednobitowy strumień szeregowy o częstotliwości 125 MHz.

- Konwerter NRZI – dzięki któremu odtwarzany jest ciąg bitowy zakodowany poziomem, a nie zmianą stanu.

- Układ SIPO: na którego wyjściu otrzymuje się 5-bitowy równoległy sygnał z zegarem 25 MHz.

- Deskrambler – na którego wyjściu uzyskuje się 4-bitowe połówki bajtów przy zegarze 25 MHz.

W 4-bitowej postaci równoległej sygnał jest przekazywany przez interfejs MII do warstwy MAC.

3.2.4 Pomiary sygnałów w sieci Ethernet 100BASE-T

Ze względu na charakter sygnałów w sieciach 100BASE-TX, tj. brak widocznej przerwy podczas transmisji i związaną z tym jednakowym kształtem sygnałów w czasie transmisji i bezczynności oraz złożony algorytm kodowania zarejestrowałem jedynie kształt zmodulowanego sygnału. Charakterystycznymi elementami przebiegu, zobrazowanego na oscylogramie (Rys. 39) są:

- Trzy poziomy napięcia -1 V, 0 V, 1 V (wartości przybliżone),

- Widoczne momenty zmiany poziomu – jedynki logiczne i momenty stałego poziomu – zera logiczne,

- Zróżnicowany czas trwania pojedynczego pełnego okresu, nie krótszy niż 26,6 ns (częstotliwość nie większa niż 37,5 MHz)

Rys. 39 Trójpoziomowa modulacja MTL-3 w Ethernecie 100BASE-TX [opracowanie własne]

Próba zdekodowania trzech bajtów informacji zobrazowanych na powyższym oscylogramie: 00011110 11110011 01011100. Rejestracja przebiegów we wszystkich czterech parach wykazuje, że transmisja odbywa się zgodnie z standardem w dwóch parach przewodów.

Kanał pierwszy posłużył do rejestracji sygnału z pary 1-2, drugi pary 3-6, trzeci 4-5 zaś czwarty pary 7-8. Wyniki pomiaru podczas dwukierunkowej transmisji danych przedstawia rysunek (Rys. 40). Pomiaru tego dokonałem przy wyłączonym komputerze, w czasie kiedy karta zasilana napięciem trybu gotowości utrzymywała połączenie z przełącznikiem w celu umożliwienia działania funkcji zdalnego uruchamiana stacji (ang. Wake On Lan).

Rys. 40 Rejestracja sygnału 100BASE-TX w czterech parach kabla [opracowanie własne]

W ramach pomiarów sygnałów w Ethernecie 100BASE-TX postarałem się zobrazować zjawisko tłumienia sygnału przez kabel oraz zjawisko opóźnienia propagacyjnego. Do przeprowadzenia eksperymentu użyłem dwóch kart wyposażonych w transformatory z odczepami i gniazda pomiarowe oraz 80 m odcinka kabla kategorii 5e z wtykami RJ-45 (w konfiguracji kabla przekrosowanego). Rejestracji dokonałem w dwóch kanałach oscyloskopu. Pierwszy kanał został użyty do rejestracji sygnału na wyjściu nadajnika pary 1-2, zaś drugi, o identycznym wzmocnieniu do rejestracji sygnału na wejściu odbiornika drugiej karty, tj. pary 3-6. Wyliczony z pomiarów (pomiary dokonane przy użyciu funkcji Vpp i Vamp oscyloskopu) spadek amplitudy sygnału prezentuje rysunek (Rys. 41).

80-cio metrowy odcinek kabla tłumi ponad 75% sygnału. Opóźnienie propagacji zmierzyłem przy użyciu markerów czasu x1, x2 odnajdując zbocza charakterystycznych fragmentów przebiegu zarejestrowanego na obu końcach kabla. Opóźnienie to wynosi 408ns (5,1 ns/metr). Wynik pomiaru czasu propagacji prezentuje rysunek (Rys. 42).

Rys. 41 Tłumienie sygnału 100BASE-TX w 80 m odcinku kabla CAT5e [opracowanie własne]

Rys. 42 Opóźnienie propagacyjne w 80 m odcinku kabla CAT 5e [opracowanie własne]

3.3 Standard 1000BASE-T

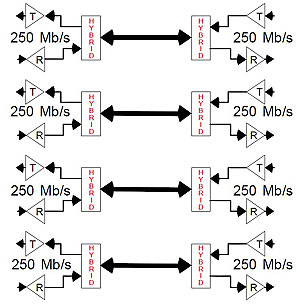

Zasadniczą zmianą, jaką zaproponowano w momencie opracowywania standardu dla sieci gigabitowej na miedzi, było wykorzystanie wszystkich czterech par kabla skrętkowego, zamiast dwóch par jak dotychczas oraz zastosowanie dupleksu na każdej z par (Rys. 43). Rozwiązania te nie były przełomowe, bowiem w sieciach stumegabitowych z powodzeniem zastosowano każde z tych rozwiązań z osobna55. Jako sposób kodowania sygnałów elektrycznych zastosowano również znany z starszego rozwiązania system impulsowej modulacji pięciopoziomowej PAM-556, z tą różnicą, że zastosowano pięciokrotnie większą szybkość zegara.

Rys. 43 Koncepcja podwójnego dupleksu na czterech parach57

Z punktu widzenia organizacji warstwowej i jej zgodności z modelem ISO/OSI zachowano całkowitą zgodność ze standardem 100BASE-T. Jedyną różnicą jest specyfikacja interfejsu gigabitowego GMII (ang. Gigabit Media Independent Interface), zastępującego dotychczasową specyfikacje interfejsu MII (Rys. 44).

Rys. 44 Ewolucja interfejsów pomiędzy PHY i MAC - AUI, MII, GMII58

3.3.1 Budowa kontrolera Ethernet 1000BASE-T

Postęp w dziedzinie budowy układów scalonych pozwolił na masową produkcję układów, zdolnych do pracy z większą szybkością, dla których obróbka, modulacja PAM-5, proces kodowania i skramblingu nie były przeszkodą. Ze względu na transmisję na wszystkich parach oraz wyższą częstotliwość sygnału istotne okazało się zapewnienie lepszych parametrów kabla. Przewody kategorii 5 często okazywały się niewystarczające ze względu na zbyt małą wartość parametru ACR59, choć często instalacje kategorii 5 o przewodach wykonanych w wyższej niż wymagała norma jakości nadaje się do pracy 1000BAE-T. Kable kategorii 5e rozwiązują problem zbyt małego ACR dla częstotliwości Gigabit Ethernetu.

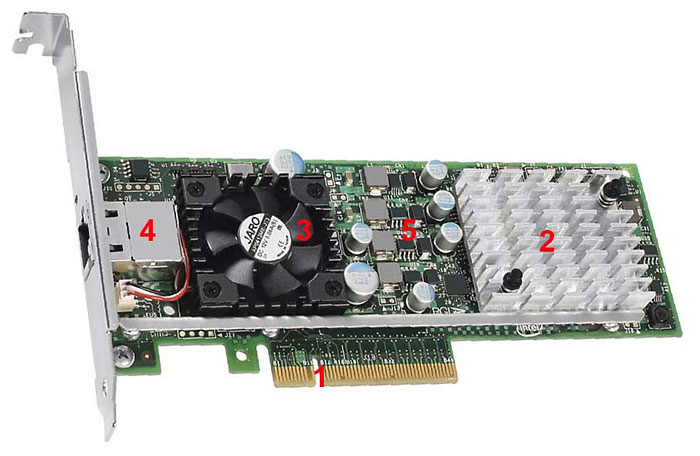

Fot. 24 Karta sieciowa - kontroler Ethernet 10/100/1000BASE-T - INTEL PRO 1000GT [fot. własna]

Powyższe zdjęcie prezentuje typowe rozwiązanie popularnej karty sieciowej 1000BASE-T Intel Pro 1000GT, zdolnej również do pracy w trybach 100BASE-TX i 10BASE-T.

Na fotografii (Fot. 24) oznaczyłem cyframi następujące elementy:

- złącze magistrali PCI,

- układ kontrolera Ethernet,

- rezonator kwarcowy,

- hybrydowy układ transformatorów i filtrów,

- gniazdo RJ-45,

- elementy stabilizatora napięcia zasilającego kontroler.

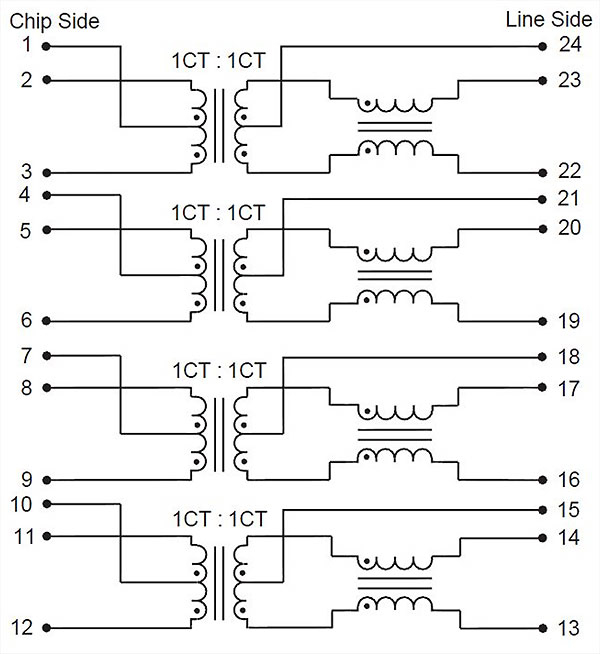

Fakt użycia czterech par w obu kierunkach wymusił zmiany w konstrukcji układu transformatorów i filtrów. Obecnie niezbędne stało się zastosowanie dwukrotnie większej liczby elementów indukcyjnych i wykonanie filtrów identycznych dla każdej pary60. Schemat przykładowego rozwiązania prezentuje schemat (Rys. 45).

Rys. 45 Schemat ideowy wnętrza układu hybrydowego BEL S558-5999-T4 M861

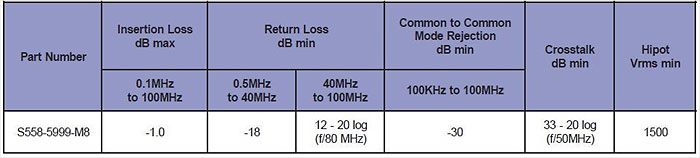

Zmianie uległ również zakres pasma przenoszenia i wymagane tłumienia przesłuchów i zakłóceń współbieżnych. Parametry gwarantowane dla przedstawionego powyżej układu, przy zapewnieniu prądu zasilania nadajnika linii 8 mA zawiera tabela 6.

Tab. 6 Zestawienie parametrów elektrycznych układu hybrydowego BELL S558-5999-T4 M862

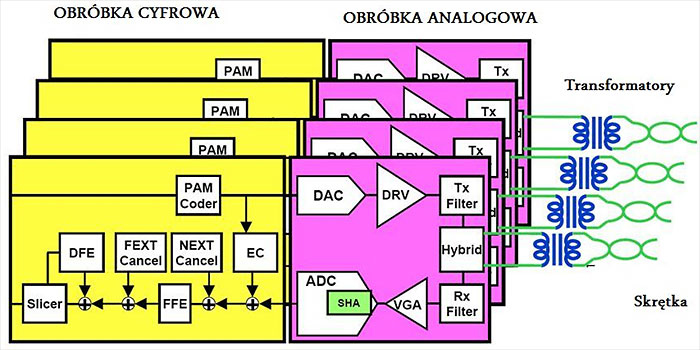

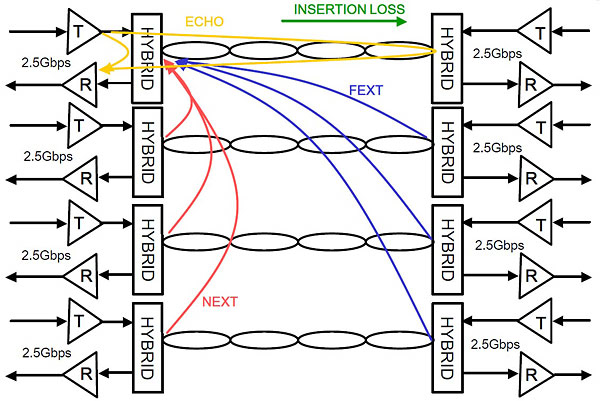

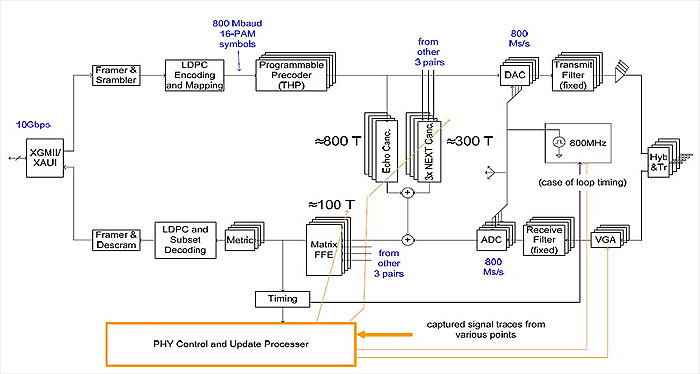

Wewnątrz układu scalonego kontrolera znajdują się cztery identyczne układy złożone z koderów PAM-5 po stronie odbiorczej, filtrów cyfrowych usuwających zakłócenia NEXT i FEXT, układów odejmujących własny sygnał nadawany od całkowitego sygnału, dekoderów PAM-5 oraz przetworników A/D i D/A, wzmacniaczy wejściowych i wyjściowych. Schemat blokowy takiego układu, z wyróżnieniem części cyfrowej i części analogowej wraz z przetwornikami prezentuje rysunek (Rys. 46). Wszystkie etapy obróbki następują analogicznie jak dla 100BASE-TX, z tą różnicą, że w torze odbiorczym konieczne jest usunięcie własnego sygnału (ta właściwość transmisji uniemożliwia zaobserwowanie sygnału tylko jednej stacji na parze przewodów – sygnał obserwowany w torze będzie wypadkową sygnałów obu stacji).

Rys. 46 Budowa wewnętrzna kontrolera 1000BASE-T63

Legenda:

- DAC – (ang. Digital to Analog Converter) – przetwornik cyfrowo-analogowy,

- DRV – (ang. Driver) – wzmacniacz wyjściowy,

- ADC - (ang. Analog to Digital Converter) – przetwornik analogowo-cyfrowy,

- FFE – (ang. Feed-Forward Equalizer) – korektor cyfrowy ze sprzężeniem i przewidywaniem64,

- VGA – (ang. Variable Gain Amplifier) – wzmacniacz o regulowanym wzmocnieniu,

- DFE – (ang. Decision-Feedback Equalizer) – korektor cyfrowy z układem adaptacyjnym65.

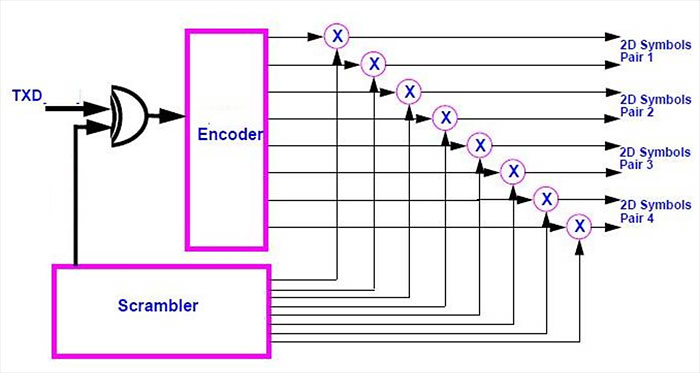

Każdy z czterech kanałów przesyła strumień 125 Mb/s w każdym kierunku, otrzymując dane ze skramblera rozdzielającego przesyłane dane na cztery symbole. Przykładowy układ logiczny skramblera prezentuje rysunek 47.

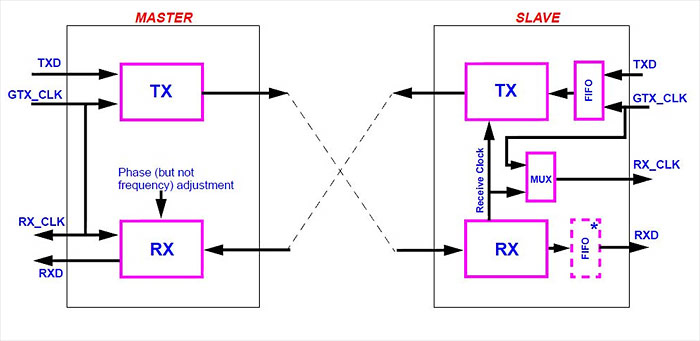

Rys. 47 Ilustracja przykładowego mechanizmu działania skramblera w 1000BASE-T66

Rozwiązanie takie powoduje, że w jednostce czasu fragmenty bajtów przesyłane są w rozbiciu na cztery pary, co skutkuje koniecznością buforowania odbieranych symboli, ich synchronizacji i składania po stronie odbiorczej. Wymusza to rygorystyczne wymagania co do różnicy opóźnień w transmisji na poszczególnych parach. Aby sprostać temu problemowi, transmisją w Gigabit Ethernecie steruje jedno z urządzeń, nadające zegar transmisyjny (urządzenie Master – zazwyczaj wieloportowe, np. przełącznik), zaś drugie (urządzenie Slave, np. karta sieciowa) synchronizuje swój zegar za pomocą pętli PLL do urządzenia nadrzędnego (Rys. 48).

Rys. 48 Ilustracja synchronizacji master-slave w 1000BASE-T67

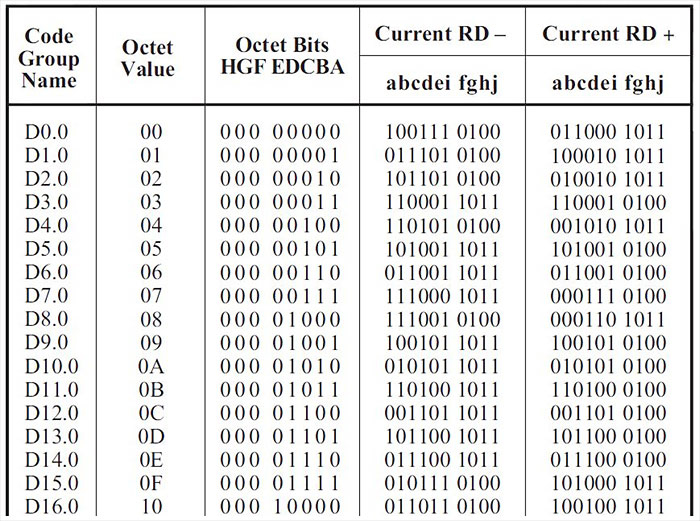

Do celów kodowania transmisyjnego w podwarstwie PCS68 zastosowano nowocześniejszy niż używany w 100BASE-TX kod strumieniowy, mianowicie kod 8B/10B opracowany w laboratoriach firmy IBM, który powoduje taki sam narzut informacji w kanale (20%), jednakże jest lepiej zbalansowany pod względem ilości występowania ciągów bitowych o tej samej wartości69. Kodowanie odbywa się w nim dwuetapowo, za pomocą zespołu przerzutników, co pozwala osiągnąć wysoką wydajność bez potrzeby angażowania mocy obliczeniowej. Fragment tablicy kodowej 8B/10B prezentuje poniższa tabela.

Tab. 7 Fragment tablicy kodowej dla kodu 8B/10B70

Ze względu na konieczność zachowania zgodności ze standardami Ethernetu i Fast Ethernetu, a w szczególności obsługi mechanizmu rywalizacyjnego dostępu do medium CSMA/CD w 1000BASE-T zastosowano rozwiązanie wydłużania ramek (Jeżeli minimalna długość ramek, pozostałą by taka sama – 64 bajty, długość segmentu sieci musiała by być skrócona do 10 m). Rozwiązanie to polega na wprowadzenia sztucznego wydłużenia krótszych ramek (ang. Carrier Extension), do 512 bajtów. Dodatkowe bajty rozszerzenia (maksymalnie 448 bajtów) dodawane są na końcu ramki i transmitowane wraz z nią, zaś po odebraniu przez stację odbiorczą są usuwane już na poziomie podwarstwy PCS, w związku z czym wyższe warstwy nie zauważają dodatkowych bajtów71. Rozwiązanie to ma istotną wadę. W przypadku transmisji małych porcji informacji, przepustowość łącza znacząco spada, w skrajnym przypadku nawet ośmiokrotnie. Rozwiązaniem tego problemu jest łączenie ramek w potoki. Aby utworzyć potok ramki się buforuje przed nadaniem, następnie pierwszą z ramek rozszerza się do 512 bajtów (w razie konieczności|), kolejne zaś dodaje z minimalnym odstępem między pakietami IPG (ang. inter packet gap). Długość tak przygotowanej ramki może wynosić maksymalnie 1500 bajtów co pozwala na znaczne poprawienie wykorzystania łącza.

Kolejnym rozwiązaniem, poprawiającym efektywność przesyłania informacji przez łącza gigabitowe jest opracowana przez firmę Alteon technologia „Jumbo Frames”. Rozwiązanie to polega na rozszerzeniu ramek do 9018 bajtów opatrzonych pojedynczym nagłówkiem, co dzięki zlikwidowaniu części odstępów między ramkami i zminimalizowaniu narzutu sygnalizacyjnego. Zauważono, że mniej nagłówków w stosunku do ilości przesyłanych informacji to prostsza, mniej obciążająca obsługa72 dzięki zmniejszeniu ilości przerwań, obliczeń i operacji trasowania. Przyrost prędkości przy taki rozwiązaniu jest znaczny, warunkiem jego użycia jest implementacja mechanizmu Jumbo Frames we wszystkich współpracujących urządzeniach.

3.3.2 Droga sygnału nadawanego i odbieranego

W stosunku do starszych rozwiązań, w sieci 1000BASE-T zaszło niewiele zmian w metodyce obróbki sygnałów. Zastosowanie innego mechanizmu kodowania czy zwiększenie liczby kanałów, w których równolegle przesyła się symbole, jest rozwiązaniem bardziej ewolucyjnym niż przełomowym. Kolejność operacji przetwarzania jest identyczna jak w 100BASE-TX z następującymi zmianami:

- Bezpośrednio za układem transformatorów znajduje się sprzęgacz – separator, który powoduje, że nadawanie i odbieranie sygnałów odbywa się w tym samym czasie na parze przewodów.

- W odbiorczej części cyfrowej pojawiły się dodatkowe filtry, oparte na technologii DSP usuwające sygnał z własnego nadajnika oraz efekty przesłuchów NEXT i FEXT.

- Układ skramblera, oprócz funkcji pełnionej w 100BASE-T, użyty jest do podzielnia strumienia informacji na cztery strumienie o mniejszej szybkości, zaś deskrambler ich ponowne złożenie.

- Układ synchronizacji zegara zapobiega błędom transmisji wynikłym z przesunięć czasowych symboli przesyłanych parami o różnych długościach73.

3.3.3 Pomiary sygnału w sieci Ethernet 1000BASE-T

Ze względu na charakter sygnałów w sieciach 1000BASE-TX, tj.:

- brak widocznej przerwy podczas transmisji i związaną z tym jednakowym charakterem sygnałów w czasie transmisji i bezczynności,

- złożony algorytm kodowania,

- zastosowanie jednoczesnego dupleksu na wszystkich parach

zarejestrowałem jedynie kształt zmodulowanego sygnału. Charakterystycznymi elementami przebiegu zobrazowanego na oscylogramie (Rys. 49) są:

- trzy poziomy napięcia -2, -1, 0, 1, 2 V (wartości przybliżone),

- widoczne rozmyte momenty zmiany poziomu,

- zróżnicowany czas trwania pojedynczego pełnego okresu, nie krótszy niż 16ns (częstotliwość nie większa niż 62,5 MHz). Czas trwania pojedynczego symbolu 8 ns.

Rys. 49 Pięciowartościowa modulacja PAM-5 w Ethernecie 1000BASE-T [opracowanie własne]

Sygnał o identycznej budowie zaobserwowałem na wszystkich czterech parach. Ze względu na transmisję dupleksową i brak możliwości oddzielenia sygnału jednej stacji (proces odejmowania własnego sygnału od sygnału odebranego odbywa się wewnątrz układu kontrolera) niemożliwym jest zdekodowanie bitów informacji z oscylogramu. Kanał pierwszy posłużył do rejestracji sygnału z pary 1-2, drugi pary 3-6, trzeci 4-5 zaś czwarty pary 7-8. Wynik rejestracji sygnałów we wszystkich parach prezentuje rysunek (Rys. 50).

Rys. 50 Rejestracja sygnału 1000BASE-T w czterech parach kabla [opracowanie własne]

Pomimo wielokrotnych prób nie udało mi się zaobserwować faktu używania tylko trzech poziomów napięcia (-2, 0, 2V) podczas synchronizacji74 odbywającej się w trakcie bezczynności łącza.

3.4 Standard 10GBASE-T

Pomimo że jeszcze w 2002 roku zakładano, że 10-cio gigabitowy Ethernet będzie funkcjonował tylko z wykorzystaniem mediów światłowodowych75, w rok później76 rozpoczęto prace nad stworzeniem standardu dla kabli miedzianych77. Zastosowano w nim rozwiązania układowe i funkcjonalne znane z 1000BASE-T:

- transmisja na wszystkich czterech parach w obu kierunkach,

- zarządzanie zegarem przez stację główną (zazwyczaj urządzenie wieloportowe),

- usuwanie przesłuchów, echa na drodze cyfrowej filtracji za pomocą DSP.

Zmianie zaś uległy:

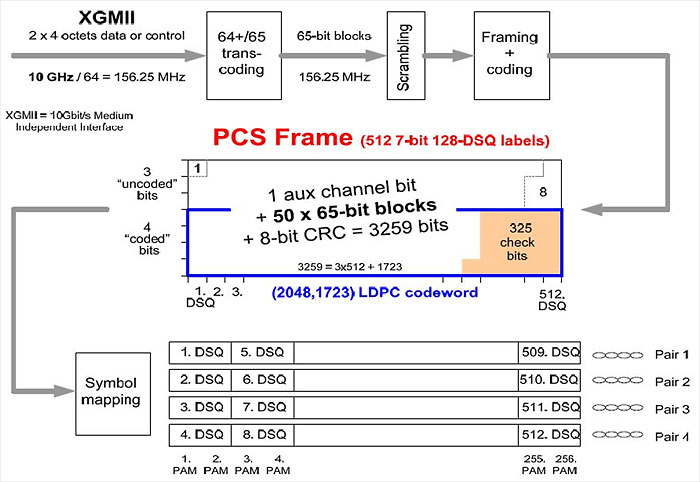

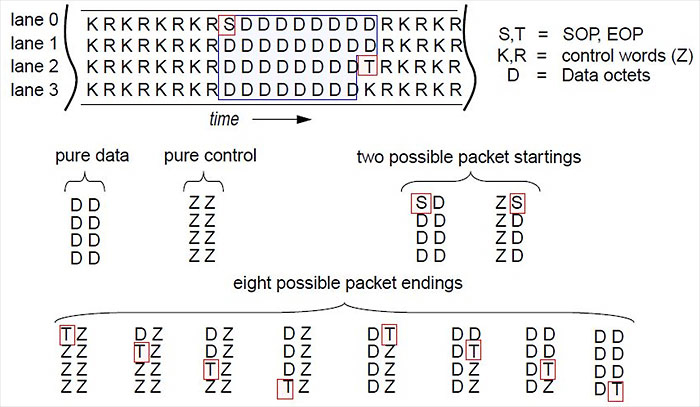

Z punktu widzenia organizacji warstwowej i jej zgodności z modelem ISO/OSI zachowano całkowitą zgodność ze standardem 1000BASE-T80, specyfikując interfejs dziesięciogigabitowy XGMII (ang. Ten Gigabit Media Independent Interface) zastępujący dotychczasową specyfikacje interfejsu GMII. Nowością stało się wyróżnienie dwóch rozwiązań podwarstwy zależnej od medium, oddzielnie dla sieci lokalnych i dla sieci WAN81. W rozwiązaniu dla sieci WAN specyfikuje się dodatkową podwarstwę WIS (ang. Wan Interface Sublayer) przeznaczoną do realizacji funkcji zarządczych w sieciach SONET/SDH. Podstawową jej funkcją jest ramkowanie (ang. framing) wynikłe z konieczności podziału słów 66-bitowych, charakterystycznych dla 10 GbE na 16-bitowe, stosowane w SONET/SDH.

Przez XGMII dane przesyła się równolegle 32-bitowymi magistralami w kierunku nadawania i odbioru. Z uwzględnieniem niezbędnych sygnałów sterujących i taktujących złącze zawiera 74 linie. Ze względu na stopień komplikacji interfejsu XGMII IEEE opracowało również prostszy w obsłudze interfejs XAUI (ang. Ten Gigabit Attachment Unit Interface). Ta uproszczona wersja złącza XGMII zadowala się zaledwie 16 liniami. Samotaktująca magistrala opiera się bezpośrednio na standardzie 1000BASE-X, ale przewody danych eksploatowane są z dwuipółkrotną szybkością, a więc 2,5 Gb/s. W ten sposób czterema równoległymi parami przewodów można przesłać 10 Gb/s. Ponadto XAUI wykorzystuje znane z 1000BASE-X starsze i prostsze rozwiązanie kodowania, mianowicie 8B/10B. Złącze charakteryzuje się wysoką tolerancją elektromagnetyczną, stosunkowo dużą stabilnością w zakresie różnic czasów przebiegu i odpornością na zakłócenia przesyłu.

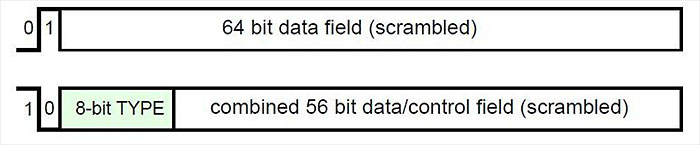

Kod 64B/66B, opracowany i zaproponowany do zastosowania w 10-gigabitowym Ethernecie w 2000 roku przez firmę Agilent82, cechuje się nadmiarowością znacznie mniejszą, niż kody 4B/5B czy 8B/10B. Powoduje zaledwie 3.125% narzutu informacji w kanale w stosunku ilości przesłanych danych. Posiada cechy samokontroli dzięki zastosowaniu 4-bitowego kodu Hamminga83 i wplecionych w strukturę ramek słów kontrolnych.

Kodowanie korzysta z dwóch typów ramek, przeznaczonych do transmisji samych danych, jak również do przesyłu danych wraz kodami kontrolno-sterującymi. Strukturę ramek prezentuje rysunek (Rys. 51).

Rys. 51 Struktura ramki danych (góra) i danych wraz kodami sterującymi (dół)84

Tak jak w starszych wersjach standardu Ethernet układ skramblera powoduje zawężenie widma sygnału, poprzez zmieszanie z ciągiem pseudolosowym. Nowością jest układ oznaczony na rysunku (Rys. 52) „Framing + Coding”. Jest to zespół przekształceń, obejmujący swoim zakresem zarówno kodowanie 128DSQ85, jak i optymalizację przebiegu LDPC86 za pomocą wstępnego mapowania THP Thomilson-Harashima87 (opisane w dalszej części pracy)88.

Jako format modulacji sygnału dla 10 Gb/s Ethernetu wybrano system PAM-16. Jest to rozwiązanie analogiczne do zastosowanego w 1000BASE-T, jednakże w celu zakodowania symboli posługuje się szesnastoma poziomami napięcia z zakresu -2 V do 2 V.

Rys. 52 Koncepcja kodowania i modulacji sygnału w 10GBASE-T89

Ostatnim etapem kodowania jest rozdzielenie sygnału na cztery strumienie, przeznaczone do wysłania przez pary skręcone za pomocą mapowania Hari (Rys. 53), zmodulowanie ciągu bitowego za pomocą modulatora PAM-16, odfiltrowanie wyższych harmonicznych, wzmocnienie i dostarczenie sygnału do sprzęgacza współpracującego z transformatorem liniowym.

Rys. 53 Mapowanie Hari w 10GBASE-T90

Większa częstotliwość i mniejszy odstęp pomiędzy wartościami napięć użytymi do kodowania informacji niż w 1000BASE-T spowodowały, że pojawiły się kolejne czynniki, które mają istotną rolę w degradacji przesyłanych sygnałów. O ile w sieciach gigabitowych o możliwości nawiązania połączenia decydowały przesłuchy zbliżne, ACR i Echo, o tyle w sieciach gigabitowych zaczął być odczuwalny przesłuch zdalny (FEXT, ELFEXT), przesłuchy z sąsiednich kabli ANEXT, AFEXT91 (ang. Alien Crosstalk) oraz przenikanie zakłóceń EMI/RFI92. Źródła i drogi wnikania zakłóceń w kabel prezentuje rysunek 54.

Rys. 54 Przyczyny zakłóceń w sieci 10GBASE-T93

Spowodowało to konieczność zastosowania kabli o podwyższonych parametrach tłumienia zakłóceń i mniejszym tłumieniu własnym. Ze względu na to, że jak potwierdziły badania94, długość większości kabli (99,3%) stosowanych w instalacjach nie przekracza 55 m (Tab. 8) zaproponowano dwa standardy okablowania, kategorię 6 i 6a, przeznaczone do stosowania w sieciach 10GBASE-T na odległościach odpowiednio do 55 i do 100 m.

Tab. 8 Długości kabli w typowych sieciach lokalnych95

Zwiększenie częstotliwości sygnału i szerokości widma pociągnęło za sobą konieczność dostosowania parametrów transformatorów liniowych, w szczególności w zakresie pasma przenoszenia (do 500 MHz) i zwiększenia tłumienia przesłuchów pomiędzy parami (do 50 dB)96. Parametry przykładowego wykonania zespołu transformatorów firmy E&E zawiera tabela 8, zaś schemat ideowy połączeń wewnętrznych hybrydowego gniazda z zespołem filtrów i transformatorów, oferowanego przez firmę Pulse prezentuje rysunek (Rys. 55).

Tab. 9 Zestawienie parametrów elektrycznych układu hybrydowego 97

Schemat połączeń wewnętrznych układu hybrydowego uległ zmianie. Dodano dodatkowe uzwojenie w układzie filtra zakłóceń współbieżnych, aby zapobiec przenikaniu sygnałów między parami poprzez punkt swobodnej masy.

Rys. 55 Schemat wewnętrznej budowy gniazda RJ-45 zintegrowanego z transformatorami i filtrami98

3.4.1 Budowa kontrolera Ethernet 10GBASE-T

Na poniższej fotografii znajduje się karta sieciowa Intel 10 Gigabit AT99. Jest to produkt stosunkowo nowy, wprowadzony na rynek na początku 2008 roku. Większość elementów karty jest zasłonięta przez elementy odprowadzające ciepło, co spowodowane jest dużym poborem mocy, zarówno przez układ DSP, jak i kontroler (Pobór mocy szacowany jest na poziomie 25 W). Dla sprostania wymogom zasilania producent zastosował układ czterofazowej, impulsowej przetwornicy napięcia obniżającej napięcie 3,3 V dostępne na magistrali PCI Express do 1,8 V.

Fot. 25 Karta sieciowa - kontroler Ethernet 10GBASE-T - INTEL 10 Gigabit AT100

Na fotografii (Fot. 25) oznaczyłem cyframi następujące elementy:

- złącze magistrali PCI Express 8x,

- procesor DSP z radiatorem – kontroler 10GBASE-T,

- przetwornik ADC z aktywnym układem chłodzenia

- gniazdo RJ-45 zintegrowane z zespołem filtrów i transformatorów,

- elementy impulsowej przetwornicy napięcia,

- elementy stabilizatora napięcia zasilającego kontroler.

Zastosowanie magistrali PCI Express 8x zostało podyktowane koniecznością dopasowania przepustowości magistrali do prędkości 10 Gb/s – starsze rozwiązania, np. PCI nie gwarantowały tak wysokich przepływności.

Na schemacie blokowym (Rys. 56) wyróżniono podział bloków funkcjonalnych na dwa układy scalone. Część elementów toru odbiorczego, jak przetwornik analogowo-cyfrowy, filtr, zespół pętli PLL i ich elementy sterujące, została wydzielone w osobnym układzie. Pozostałe bloki układu odbiorczego związane z korekcją echa i przesłuchów oraz dekoder i deskrambler znajdują się wewnątrz układu DSP. Na schemacie widoczny jest również dodatkowy przetwornik cyfrowo-analogowy w torze odbiorczym, co jest spowodowane koniecznością wprowadzenia do układu sprzęgacza/rozdzielacza (zawierającego wzmacniacz o małym poziomie szumów własnych LNA – ang. low noise amplifier) własnego sygnału nadawanego w przeciwfazie z odpowiednią amplitudą, aby wstępnie wyeliminować echo i NEXT. Ponieważ jednak taki mechanizm nie działa idealnie, tłumienie echa jest wspomagane przez cyfrowe przetwarzanie sygnału na poziomie przetwarzania w DSP.

Rys. 56 Koncepcja schematu blokowego kontrolera Ethernet 10GBASE-T101

Elementy toru nadawczego zostały oznaczone kolorem czerwonym, odbiorczego fioletowym. Pasywne elementy – gniazdo RJ-45 i hybrydowy zespół transformatorów – zielonym, zaś kontrolne i sterujące białym.

3.4.2 Droga sygnału nadawanego i odbieranego

Uproszczony schemat blokowy (Rys. 57) obrazuje kolejność przekształceń sygnału nadawanego i odbieranego, jak również sprzężenie pomiędzy układami nadajnika i odbiornika, niezbędne dla eliminacji zakłóceń.

„Na początku informacje trafiają do enkodera PCS. Otrzymuje on osiem bajtów danych przez 32-bitową magistralę w dwóch następujących po sobie porcjach. Przesłanie całego pakietu 64 bitów informacji poprzedza bit kontrolny. Pozwala to na zmniejszenie zakłóceń. Dane wejściowe są mieszane w scramblerze z ciągiem pseudolosowym, w wyniku czego sygnał zamieniany jest w długą sekwencję przypominającą szum. Jego energia jest równomiernie rozłożona w całym spektrum transmisyjnym; przy dłuższych ciągach jedynek lub zer w danych użytkowych nie dochodzi do powstawania w kablu stałych poziomów dodatnich lub ujemnych, które mogłyby zablokować wejście karty sieciowej.

Rys. 57 Uproszczony schemat podwarstwy PMD w 10GBASE-T102

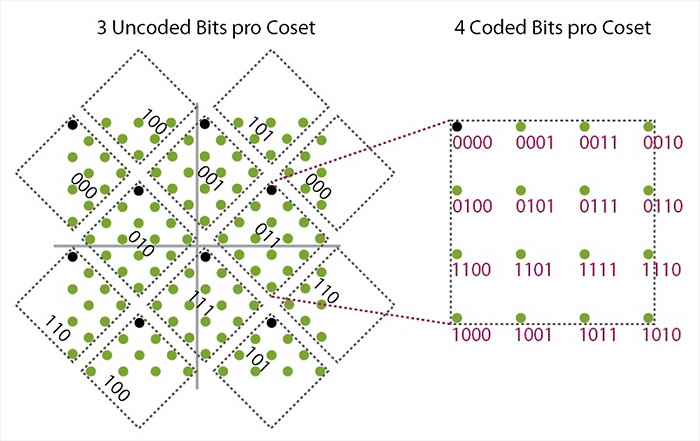

Na poszczególnych parach żył nie pojawiają się też takie same symbole, co pozwala z jednej strony przeciwdziałać przekłamaniom w transmisji, a z drugiej – ograniczyć zjawiska echa oraz przesłuchów” (4). Za scramblerem najpierw zbierane jest pięćdziesiąt 65-bitowych pakietów (bloków) danych, które tworzą część danych użytkowych ramki 10GBASE-T. Przed nimi umieszcza się tzw. Auxiliary Channel Bit, a za nimi – ośmiobitową sumę kontrolną (pole CRC). Ramka składa się zatem z 3259 bitów. Muszą być one jedynie transponowane (zakodowane) na odpowiednie symbole, a następnie rozdzielone na cztery pary żył. 10GBASE-T stosuje kodowanie 128-DSQ (ang. Double Square), co pozwala na zapisanie siedmiu bitów informacji w jednym symbolu. Siedmiobitowe porcje danych są tworzone z zestawów cztero- i trzybitowych (Rys. 58).

Rys. 58 Konstelacja kodu 128DSQ103

Część strumienia danych jest zabezpieczona przed pojawieniem się przekłamań z wykorzystaniem LDPC (wstępna korekcja błędów, FEC, 1723 kodowanych bitów na ramkę. Miejsce kodowania LDPC w strukturze obróbki sygnału 10GBASE-T obrazuje rysunek 52). Taka obróbka dotyczy porcji czterobitowych, znajdujących się w jednej grupie. Kodowanie z wykorzystaniem metody 128-DSQ pozwala obniżyć częstotliwość sygnału nośnego do poziomu 400 MHz (Rys. 59). Po zastosowaniu 128-DSQ symbole czterobitowe są opisywane w grupach złożonych z szesnastu elementów. Prekodery Tomlinson-Harashima (THP) odpowiadają za to, by skoki sygnału na wyjściu nie były za wysokie. Pozwala to na obniżenie zakłóceń sygnału, które powstają w wyniku pojawiania się echa na kablu (interferencja międzysymbolowa, (ang. Intersymbol Interference). Następnie symbole są przetwarzane przez cyfrowy filtr, który podwyższa częstotliwość sygnału w celu dostosowania urządzeń do wymogów kompatybilności elektromagnetycznej. Na koniec cztery przetworniki cyfrowo-analogowe przekształcają symbole PAM16 w szesnastopoziomowy sygnał elektryczny104.

Rys. 59 Kodowanie LDCP w 10GBASE-T105

Zestawienie połączenia w 10GBASE-T wymaga specjalnej procedury synchronizacyjnej, wykorzystującej ramki treningowe. W pierwszym etapie na podstawie pomiaru amplitudy sygnału dostraja się wzmocnienie torów wejściowych, poziom mocy wysyłanej oraz parametry prekoderów Tomillson-Harashima. „Podczas inicjacji połączenia enkoder PCS generuje ramki kontrolne PAM2 (ang. PAM2-Trainings-Frames), które pozwalają stronie odbierającej dane na zsynchronizowanie się z nadajnikiem. Poza tym za pośrednictwem specjalnych sekwencji symboli sprawdzane jest przyporządkowanie poszczególnych par żył w kablu oraz polaryzacja. Po nawiązaniu połączenia partnerzy rozpoczynają ciągłą wymianę pełnowymiarowych ramek. Gdy należy przekazać dodatkowe symbole kontrolne, wkomponowuje się je w normalny ciąg ramek. W 10GBASE-T długość ramki potrzebnej do przekazania symbolu wynosi od 1,25 nanosekundy (800 megasymboli/s). Wynika z tego, że najwyższa częstotliwość w sygnale (tzw. częstotliwość Nyquista) to około 400 MHz. W związku z tym grupa robocza IEEE odpowiedzialna za standard 802.3an określiła maksymalną częstotliwość przenoszoną przez kabel skrętkowy na poziomie 500 MHz” (4).

3.4.3 Pomiary w sieci Ethernet 10GBASE-T

Ze względu na ograniczenia, które napotkałem, tj.:

- trudność z pozyskaniem kart 10 Gb/s na medium miedziane, ze względu na wysoką cenę, zwłaszcza do prób wymagających ingerencji w układ karty, mogący skończyć się jej uszkodzeniem,

- trudność z uzyskaniem dokumentacji układów nowoczesnych kart – ze względu na tajemnicę handlową rywalizujących przedsiębiorstw,

nie udało sie przeprowadzić pomiarów w sieci 10-gigabitowej.

Jest to ciekawy temat dydaktyczny, z pewnością możliwy do przeprowadzenia w przyszłości, kiedy 10-gigabitowy Ethernet się upowszechni, a w laboratoriach nastąpi modernizacja aparatury pomiarowej.

4 Autonegocjacja w rozwiązaniach sieci Ethernet bazujących na medium miedzianym

- Por. „IEEE Std 802.3™-2005 Standard for Information technology - Telecommunications and information exchange between systems Local and metropolitan area networks - Specific Requirements Part 3: Carrier sense multiple access with collision detection (CSMA/CD) access method and physical layer specifications” (97 p. 315).

- Firma 3Com produkowała przez wiele lat karty typu 3C509B na szesnastobitową magistralę ISA w trzech odmianach – 3C509-TPO dla 10BASE-T, 3C509-TPC dla 10BASE-T oraz 10BASE-2, jak również 3C509B-COMBO dla 10BASE-T, 10BASE-2 i 10BASE-5. Karty posiadały taki sam układ kontrolera, różniły się jedynie ilością podłączonych PMD. Podłączenia można było dokonać tylko do jednego, wybranego PMD – przyp. aut.

- Amerykańska firma Novell Inc, jako potentat na rynku technologii sieciowych w latach 80. i 90. wyznaczała kierunki rozwoju sieci, mające wpływ również na urządzenia dla sieci Ethernet. W początkowym okresie promowała rozwiązania 8-bitowych kart na magistrale ISA o oznaczeniu NE1000 (ang. Novell Eagle 1000), a nieco później 16-bitowych kart NE2000. Inni producenci dla zachowania zgodności stosowali się do wymagań formy Novell – przyp. aut.

- PCI (ang. Peripheral Components Interconnect) 32-bitowa magistrala systemowa komputerów PC, Mackintosh o przepustowości od 133MB/s. Taktowana w wersji podstawowej zegarem 33MHz. Wprowadzona w 1992 roku jako następca przestarzałych złącz ISA, EISA, MCA oraz VESA Local-BUS. Pa podstawie: „Anatomia PC” (59 strony 271-305).

- RAM (ang. Random Access Memory) – pamięć o dostępie swobodnym. W kontrolerze Ethernet przeznaczona była do buforowania ramek nadawanych i odbieranych oraz przechowywania rejestrów stanu kontrolera – przyp. aut.

- EEPROM (ang. Electrically Erasable Programmable Read Only Memory) – odmiana pamięci nieulotnej PROM, kasowalna w układzie za pomocą napięcia kasującego (co odróżnia ją od innych pamięci np. PROM – pamięci jednokrotnie zapisywalnych czy EPROM – pamięci programowalnych wielokrotnie, do których skasowania niezbędne jest naświetlanie promieniami ultrafioletowymi) Wytwarzana często jako układ o niewielkiej pojemności, z zapisem i odczytem szeregowym, przeznaczona do zapisywania danych konfiguracyjnych w urządzeniach techniki mikroprocesorowej – przyp. aut.

- W celu skompensowania reaktancji indukcyjnej (dodatniej), wynikłej z wprowadzenia kilkucentymetrowego odgałęzienia w torze koncentrycznym (suma długość bocznej gałęzi trójnika, długości gniazda oraz doprowadzeń) równolegle do styków gniazda dodawano kondensator, dostrajany za pomocą np. przycięcia lub doboru. Miało to za zadanie zminimalizować straty wynikające z wprowadzenia nieciągłości impedancji w linii długiej – przyp. aut.

- Dioda zenera – odmiana diody półprzewodnikowej, której głównym parametrem jest napięcie przebicia złącza p-n. Po przekroczeniu napięcia przebicia ma miejsce nagły wzrost prądu. W kierunku przewodzenia (anoda spolaryzowana dodatnio względem katody) zachowuje się jak normalna dioda, natomiast przy polaryzacji zaporowej (katoda spolaryzowana dodatnio względem anody) może przewodzić prąd po przekroczeniu określonego napięcia na złączu, zwanego napięciem przebicia. Dioda zenera spolaryzowana w kierunku zaporowym używana była w sieciach bazujących na kablu koncentrycznym jako element wykrywający wzrost napięcia w linii, świadczący o zaistnieniu kolizji – przyp. aut.

- Warystor – odmiana rezystora o rezystancji silnie uzależnionej od przekroczenia progowej wartości przyłożonego napięcia. Stosuje się go jako ochronnik przepięciowy. Przy napięciach poniżej wartości progowej charakteryzuje się rezystancją w zakresie setek kiloomów, zaś po przekroczeniu napięcia progowego jego rezystancja spada do kilkunastu omów. Pozwala to odprowadzić nadmierny ładunek elektryczny, zapobiegając uszkodzeniu innych podzespołów – przyp. aut.

- Elementy te były montowane w kartach stacji roboczych bez pamięci masowej (twardego dysku). W pamięci przechowywano program ładujący, pozwalający na załadowanie systemu operacyjnego ze zdalnego serwera poprzez sieć – przyp. aut.

- Schemat blokowy z materiałów katalogowych. Por. „CS8920A Advanced Product Databook” (49).

- Schemat ideowy z materiałów katalogowych. Por. „10BASE-T Transceiver modules” (51).

- Schematy połączeń poszczególnych elementów mogą się różnić w zależności od producenta. Ponieważ bloki funkcjonalne są zbliżone konstrukcyjnie, w celu zaprezentowania idei budowy kart sieciowych przedstawiłem schematy podzespołów różnych producentów, bazując na dostępności dokumentacji i poziomie abstrakcji wystarczającym dla objaśnienia zasady ich działania. Por. np. „LAN91C94 ISA/PCMCIA Single-Chip Ethernet Controller with RAM” (50) – przyp. aut.

- Patrz: patent USA „Lan magnetics interface circuits” (26).

- Schemat ideowy z materiałów katalogowych. Por. „10/100BASE-T Lan Magnetics Single Port Transformer Modules S558-5999-K8” (8).

- Nawinięcie bifilarne – wykonanie uzwojenia (transformatora, dławika) dwoma ściśle przylegającymi przewodami jednocześnie, w celu zapewnienia ich identycznej indukcyjności i zachowania symetrii. Rozwiązanie często stosowane w układach symetrycznych – przyp. aut.

- Na podstawie „Function of Ethernet magnetics” (15).

- Por. „IEEE Std 802.3™-2005 Standard for Information technology - Telecommunications and information exchange between systems. Local and metropolitan area networks - Specific Requirements” (97 p. Section1 160).

- Teoria budowy i działania transformatorów szerokopasmowych, transformatorów impedancji i symetryzatorów por. „Transmission Line Transformers” (45) i „Understanding, Building and Using Baluns and Ununs” (64).

- Prądy wyrównawcze – prądy, przepływające pomiędzy punktami o zróżnicowanym potencjale. W sieciach komputerowych (jak również wielu innych instalacjach) zjawisko niepożądane, będące źródłem zakłóceń, a także, przy znacznych wartościach prądów bądź napięć, mogące być powodem uszkodzeń sprzętu bądź okablowania – przyp. aut.

- Na podstawie materiałów katalogowych firmy Bel Fuse Inc. Por. „10BASE-T Network Components Quad 4-Port Module” (67).

- Schemat blokowy z materiałów katalogowych. Por. „CS8920A Advanced Product Databook” (49).

- Kod Manchester – sposób fazowej modulacji sygnału cyfrowego opracowany przez G.E. Thomasa w 1949 roku (modulacja bifazowa). W standardzie IEEE 802.3 logicznemu zeru odpowiada zmiana stanu z wysokiego na niski, zaś logicznej jedynce z niskiego na wysoki, choć pierwotnie proponowano odwrotne znaczenie zmian stanu.

- Rysunek dostępny publicznie (ang. public domain), [2006, Schmidt Stefan]. Por. [online] en.wikipedia.org: Rysunek został zweryfikowany pod względem zgodności z opisem kodowania Manchester IEEE802.3 opisanym w: „Sieci LAN, MAN i WAN – Protokoły komunikacyjne” (84) – przyp. aut.

- PLL (ang. Phase Locked Loop) pętla synchronizacji fazowej – układ elektroniczny służący do synchronizacji sygnałów elektrycznych poprzez porównanie sygnałów o zbliżonych częstotliwościach. Szeroko stosowany w elektronice i telekomunikacji. Bardzo często używany do stabilizacji pracy generatorów z wzorcami częstotliwości (np. kwarcowymi) lub do celów synchronizacji w układach komunikacyjnych. Składa się z dzielników częstotliwości, komparatora fazy (układu porównującego zgodność fazową przebiegów) , wzmacniacza błędu i układu regulującego jeden z synchronizowanych przebiegów. Pojęcie pętli wynika z faktu, że wytworzone napięcie regulacyjne, proporcjonalne do wartości błędu pomiędzy fazami porównywanych sygnałów, używane jest do przestrajania generatora dla uzyskania zgodności fazy jego przebiegu z przebiegiem wzorcowym – przyp. aut.

- Rysunek z prezentacji. Por. „8B/10B Coding, 64B/66B Coding” (35).

- Filtr aktywny – filtr zrealizowany przy użyciu elementu wzmacniającego, z sprężeniem zwrotnym. Jego zastosowanie pozwala na uzyskanie większego nachylenia charakterystyki niż w przypadku filtrów pasywnych zbudowanych tylko z elementów R L C. Ważną cechą jest możliwość wpływania na charakterystykę filtru aktywnego poprzez regulacje na drodze elektronicznej, np. zmianę napięcia – przyp. aut.

- Schemat blokowy z materiałów katalogowych. Por. „CS8920A Advanced Product Databook” (49).

- Tłumaczenie rysunku z materiałów katalogowych „ML4658 10BASE-T Transceiver” (20).

- Schemat blokowy z materiałów katalogowych. Por. Tamże.

- Rysunek z materiałów katalogowych: „CS8920A Advanced Product Databook” (49).

- Tłumaczenie własne, rysunek na podstawie: „8B/10B Coding, 64B/66B Coding” (35).

- Rysunek na podstawie: „WARP - The UTP Technology for 10GBASE-T” (38).

- Schemat blokowy z materiałów katalogowych. Por. „LAN8700 / LAN8700i 15kV ESD Protected MII/RMII 10/100 Ethernet Transceiver with HP Auto-MDIX and flexPWR technology in a small Footprint” (7).

- 4B/5B – liniowy kod transmisyjny, spopularyzowany w 1995 roku za sprawą rozwiązania FDDI, opisany bardziej szczegółowo w dalszej części niniejszejszego opracowania.

- Skrambler (ang. Scrambler) – układ powodujący sumowanie przebiegu użytecznego z pseudolosowym ciągiem za pomocą operacji różnicy symetrycznej XOR w celu uzyskania sekwencji kodowej o zmniejszonej długości ciągu o tej samej wartości bitowej. Stosowany jest w układach transmisji szeregowej, aby zapewnić możliwość synchronizacji zegara transmisyjnego po stronie odbiorczej i zniwelować ryzyko strat sygnału przy przesyłaniu przez indukcyjne i pojemnościowe elementy toru transmisyjnego, zawęzić pasmo wymagane do przeniesienia sygnału użytecznego oraz zminimalizować poziom zakłóceń i przesłuchów. W torze odbiorczym niezbędne jest odwrócenie tej operacji przy użyciu analogicznego układu – deskramblera. Obydwa układy do pracy wykorzystują zazwyczaj rejestry przesuwne. Na podstawie „Przewodowe i bezprzewodowe sieci LAN” (43).

- PISO (ang. Parallel Input, Serial Output) – układ logiczny, przetwarzający strumień danych zakodowany na wielu równoległych n-bitach w szeregowy strumień jednobitowy o szybkości n-krotnie większej – przyp. aut.

- NRZI (ang. Non Return to Zero Inverted) – rodzaj liniowego kodowania transmisji, w którym zmiana stanu sygnału zakodowanego następuje w momencie kodowania logicznej jedynki. Logiczne zero w ciągu kodowanym nie powoduje zmiany stanu ciągu zakodowanego – przyp. aut.

- MLT-3 (ang. Multi Level Transmit) – kod trójwartościowy, w którym zmiana poziomu napięcia odpowiada logicznej jedynce, zaś brak zmiany poziomu – logicznemu zeru. W standardzie 100BASE-TX przyjęto następujące wartości napięć -1 V, 0 V, 1 V. Sposób kodowania objęty jest prawem patentowym USA. Patrz: „Method and apparatus for multilevel encoding for a local area network” (58).

- SIPO (ang. Serial Input, Parallel Output) – układ logiczny przetwarzający strumień danych zakodowany na jednym bicie równoległy, n-bitowy strumień o szybkości n krotnie mniejszej – przyp. aut.

- Por. „10/100BASE-T Lan Magnetics Single Port Transformer Modules S558-5999-K8” (8) oraz „10/100BASE-T Single port transformer modules with 1:1 Transmit turns ratios” (11).

- Na podstawie materiałów katalogowych: „RJ-45 With integrated 10/100 BASE-T Lan magnetics” (21).

- Kompilacja z materiałów katalogowych. Por. tamże.

- Tabela z materiałów katalogowych firmy BEL. Por. „10/100BASE-T Lan Magnetics Single Port Transformer Modules S558-5999-K8” (8).

- Na podstawie: „DigiConnect ME” (60).

- Rysunek z materiałów katalogowych. Por: „LAN8700 / LAN8700i 15kV ESD Protected MII/RMII 10/100 Ethernet Transceiver with HP Auto-MDIX and flexPWR technology in a small Footprint” (7).

- Por. „100BASE-X Physical Coding Sublayer (PCS)” (68).

- Na podstawie: „The Ethernet Evolution From 10 Meg to 10 Gig. How it all Works!” (37).

- Rysunek dostępny publicznie (na zasadach licencji GNU Free Documentation), por. [online]: wikimedia.org Rysunek zweryfikowany (nieujęte w spisie literatury) – przyp. aut.

- Opracowanie własne, na podstawie: „8B/10B Coding, 64B/66B Coding" (35).

- Rysunek z materiałów konferencyjnych firmy Broadcom. Por. „10GBASE-T: 10Gb/s Ethernet over copper” (89).

- Vp-p (ang. Voltage Peak-to-Peak) – amplituda napięcia, wartość międzyszczytowa – przyp. aut.

-

Rysunek z materiałów katalogowych. Por: „LAN8700 / LAN8700i 15kV ESD Protected MII/RMII 10/100 Ethernet Transceiver with HP Auto-MDIX and flexPWR technology in a small Footprint” (7).

- Opracowanie własne, na podstawie „8B/10B Coding, 64B/66B Coding" (35).

- Transmisja na czterech parach (po dwie w każdym kierunku) – 100Base-T4. Transmisja z jednoczesnym dupleksem na dwóch parach (na każdej z par w dwie strony) – 100BASE-T2. Por. rozdz. 2.2.

- Tamże.

- Rysunek poglądowy z materiałów konferencyjnych. Por. „Gigabit Ethernet 1000BASE-T” (17).

- Na podstawie: „IEEE 802.3 architecture and 40/100GbE” (71).

- Por. „Gigabit Ethernet 1000BASE-T” (17).

- Patrz: materiały katalogowe firmy BEL Fuse Inc. „Gigabit Ethernet Magnetics Single Port Transformer Modules S558-5999-T4” (18).

- Schemat z materiałów katalogowych. Por. tamże.

- Wycinek tabeli z materiałów katalogowych. Por. tamże.

- Na podstawie: „Gigabit Ethernet Signaling On Copper” (65).

- Definicje i zasady działania korektorów cyfrowych z układami adaptacyjnymi wykraczają poza zakres niniejszej pracy. Więcej informacji na temat filtrów cyfrowych – patrz: „Equalization” (87).

- Por. tamże.

- Por. „Update on QAM-Based 1000BASE-T Transceiver” (66).

- Por. tamże.

- Por. „Gigabit Ethernet 1000BASE-T Physical Coding Sublayer (PCS) Functional Basics and Overview” (61).

- Kod 8B/10B został opracowany w 1983 roku przez pracowników działu rozwoju firmy IBM – A. X. Widmer i P. A. Franaszek. W istocie jest on złożeniem kodów 5B/6B z kodem 3B/4B – patrz. „A DC-Balanced, partitioned-Block, 8B/10B Transmission Code” (47).

- Tablica kodowa 8B/10B zawiera 256 symboli reprezentujących 8-bitowe dane i 12 symboli specjalnych dla potrzeb sterowania transmisją. Fragment tablicy kodowej został zamieszczony w celach poglądowych i porównawczych. Pełna tablica 8B/10B – Patrz: „IEEE Std 802.3™-2005 Standard for Information technology - Telecommunications and information exchange between systems Local and metropolitan area networks - Specific Requirements Part 3: Carrier sense multiple access with collision detection (CSMA/CD) access method and physical layer specifications”„A DC-Balanced, partitioned-Block, 8B/10B Transmission Code” (47).

- Na podstawie: „Vademecum teleinformatyka” (106 str. 205).

- Na podstawie: Tamże, str. 206.

- Długość każdej z par w kablu wynika z różnic skoku skręcenia, który jest stosowany w celu minimalizacji przesłuchów i zakłóceń. Dopuszczalne różnice w długościach i opóźnieniach propagacyjnych zawiera norma. Por. „ANSI/TIA/EIA-568-B-2001 Commercial Building Telecommunications Cabling Standard” (77).

- W czasie bezczynności łącza, w celu poprawienia warunków synchronizacji sygnału zegarowego nadajnik 1000BASE-T używa tylko trzech poziomów napięcia (-2, 0, 2 V) aby zapewnić większą stromość zboczy, korzystnie wpływającą na precyzję działania pętli PLL w odbiorniku. Por: „IEEE Std 802.3™-2005 Standard for Information technology - Telecommunications and information exchange between systems Local and metropolitan area networks - Specific Requirements. Part 3: Carrier sense multiple access with collision detection (CSMA/CD) access method and physical layer specifications” (97) Sekcja 3, Rozdział 40.

- Por. „Przewodowe i bezprzewodowe sieci LAN” (43 str. 209)

- „Transfer z prędkością 10 Gb/s za pośrednictwem światłowodu pociąga za sobą wysokie koszty instalacji w przeliczeniu na jedno gniazdko. Na przykład koszt jednego modułu światłowodowego 10GBASE-SR dla adaptera sieciowego firmy Nortel kształtuje się na poziomie 1100 euro (model AA1403005). Dlatego właśnie pojawił się postulat wprowadzenia standardu 10GBASE-T. Przewiduje on stosowanie czteroparowej skrętki zakończonej wtyczką typu RJ45. Pozwoliłoby to na obniżenie ceny budowy sieci do poziomu jednej trzeciej kosztów instalacji światłowodowej. Pierwsze spotkanie grupy roboczej IEEE poświęcone nowej specyfikacji 802.3an odbyło się już w listopadzie 2002 roku. Szybko stało się jednak jasne, że 10GBASE-T tylko wtedy będzie realną alternatywą wobec technologii światłowodowej, jeżeli podobnie jak Gigabit-Ethernet pozwoli na łączenie punktów oddalonych od siebie o 100 metrów”. Por: „10 gigabitów na miedzianym szlaku” (4).

- Wczesne opracowania dotyczące standardu 10GBASE-T patrz: „10GBASE-T Signaling” (25), „10 Gigabit Ethernet over Twisted Pair” (10) oraz „10GBASE-T Physical layer Specifications” (55).

- FEC (ang. Forward Error Correction) – mechanizm korekcji błędów szeroko stosowany w telekomunikacji. Jego działanie polega na dodawaniu do strumienia informacji dodatkowych bitów nadmiarowych, które pozwalają po stronie odbiorczej odtworzyć informację z częściowo zniekształconego sygnału, np. FEC 7/8 oznacza, że na każde siedem bitów danych przypada jeden dodatkowy bit kontrolny. Jest to rozwiązanie efektywne przy bardzo dużych prędkościach transmisji, ze względu na mały nakład obliczeniowy (np. funkcja różnicy symetrycznej XOR), niemniej pozwala na odtworzenie ciągu zakłóconego krótkookresowo (przekłamania na poziomie pojedynczych bitów w bajcie, słowie). FEC może być zrealizowany jako kod blokowy lub strumieniowo – przyp. aut.

- „Warto tutaj zauważyć, że w Gigabit Ethernet, pomimo że przewidywana była praca półdupleksowa, w praktyce żadne z produkowanych urządzeń tego standardu nie wykorzystuje tej metody transmisji ramek”, przypis za: „Przewodowe i bezprzewodowe sieci LAN” (43 str. 209).

- Por. „IEEE Standard for Information technology - Telecommunications and information exchange between systems - Local and metropolitan area networks Specific requirements. Part 3: Carrier Sense Multiple Access with Collision Detection (CSMA/CD) Access Method and Physical Layer Specifications Amendment 1: Physical Layer and Management Parameters for 10 Gb/s Operation, Type 10GBASE-T” (96).

- Rozwiązanie przeznaczone dla światłowodowych sieci szkieletowych SONET/SDH (10GBASE-W) posiada inną, rzeczywistą prędkość transmisji, dostosowaną do specyfikacji transmisji synchronicznej OC-192/TSM-64, mianowicie 9,953 Gb/s. Por. „Przewodowe i bezprzewodowe sieci LAN” (43 strony 217-218).

- Por. Materiały konferencyjne firmy Agilent. „64b/66b low-overhead coding proposal for serial links” (46).

- Kod Hamminga – liniowy, binarny kod korekcyjny, wynaleziony w 1950 przez Richarda Hamminga, zdolny do wykrywania i korygowania błędów pojedynczych, a także wykrywania błędów podwójnych (odległość Hamminga równa 3). Kod często używany w różnych rozwiązaniach telekomunikacyjnych, wyparł rozwiązania takie jak kod parzystości, kod 2 z 5 czy powtarzanie informacji. W 10GBE wykorzystywany jest kod od odległości Hamminga równej 4, wykorzystujący dodatkowy bit kontrolny i macierz kodową 7x4 i macierz parzystości 3x7. Na podstawie: Tamże, oraz „Introduction to 10 Gigabit 64b/66b” (40).

- Por. tamże.

- 128DSQ (ang. 128 Double Square) – kodowanie dwukwadratowe pozwalające na zapisanie siedmiu bitów informacji w jednym symbolu. Więcej informacji – patrz: „10GBASE-T Coding and Modulation 128-DSQ + LDPC” (88).

- LDPC (ang. Low Density Parity-Check Code) – więcej informacji patrz: „LDPC (Low Density Parity Check) coded 128 DSQ (Double Square QAM) constellation modulation and associated labeling” (90).

- Por. „64b/66b low-overhead coding proposal for serial links” (46) oraz „Tomlinson-Harashima Precoding in Space-Time Transmission for Low-Rate Backward Channel” (82).

- Por. „10 Gigabit Ethernet over Twisted-pair Copper” (54).

- Rysunek z materiałów konferencyjnych firmy Broadcom: „10GBASE-T: 10Gb/s Ethernet over copper” (89).

- Por. tamże.

- Patrz: „An Overview of 10GBASE-T” (39).

- EMI/RFI (ang. Electromagnetic Interferences / Radio Frequency Interferences) – zakłócenia elektromagnetyczne, zakłócenia radiokomunikacyjne – przyp. aut.

- Rysunek pochodzi z materiałów konferencyjnych firmy Solarflare. Por. „How SolarFlare Communications Broke the 10Gbps on UTP Barrier” (19).

- Twierdzenie oparte na wynikach badań opublikowanych w materiałach IEEE 802.3 Working Group, 2003. Por. „Data Center Design Considerations” (56).

- Por. tamże.

- Por. „Magnetics for 10GBase-T” (29) oraz „Updates on Magnetics for 10GBASE-T” (30).

- Tabela z materiałów katalogowych. Por. „10G Base-T Single Port Magnetic Module” (78).

- Schemat zaczerpnięty z materiałów katalogowych firmy Pulse. Por. „Pulse Jack 10GBASE-T Magnetics Module” (79).

- Na podstawie materiałów katalogowych firmy Intel. Por. „10 Gigabit AT Server Adapter EXPX9501AT for 10GBASE-T” (13).

- Zdjęcie z materiałów katalogowych firmy Intel. Por. tamże.

- Rysunek z materiałów konferencyjnych. Por. „How SolarFlare Communications Broke the 10Gbps on UTP Barrier” (19).

- Schemat blokowy zaczerpnięty z materiałów konferencyjnych firmy Broadcom. Por. „10GBASE-T: 10Gbit/s Ethernet over copper” (89).

- Rysunek pochodzi z artykułu: „10 gigabitów na miedzianym szlaku” (4).

- Na podstawie: tamże oraz „10GBASE-T: 10Gb/s Ethernet over copper” (89).

- Rysunek zaczerpnięty z artykułu: „10 gigabitów na miedzianym szlaku” (4) Por. „An Overview of 10GBASE-T” (39).